| Part | ML6694 |

|---|---|

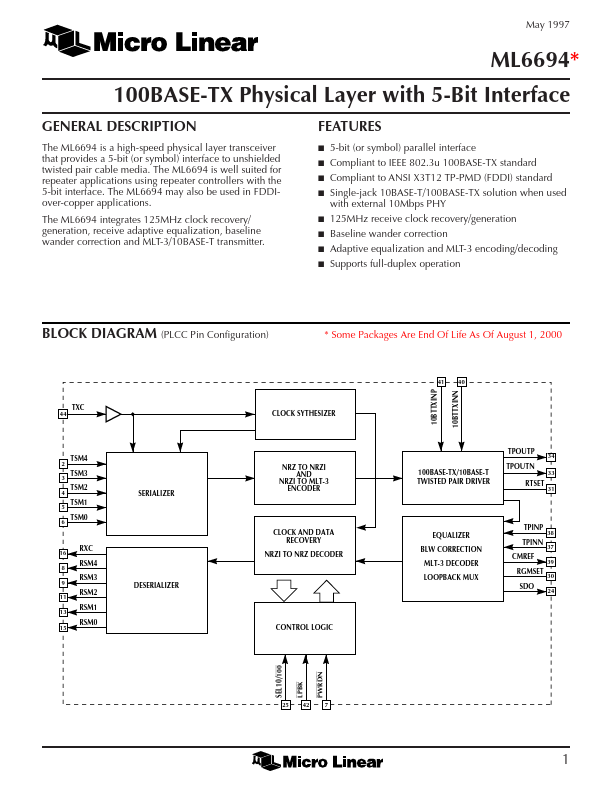

| Description | 100BASE-TX Physical Layer with 5-Bit Interface |

| Manufacturer | Micro Linear |

| Size | 177.14 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| AN214 | Microchip Technology | Smart Transducer Interface |

| AiP650E | I-CORE | 2-line Serial Interface/Common Cathode 8Seg 4Grid LED Controller/Driver |

| XT2052 | Silinktek | 1A Is Compatible With the USB Interface Linear Battery Management |