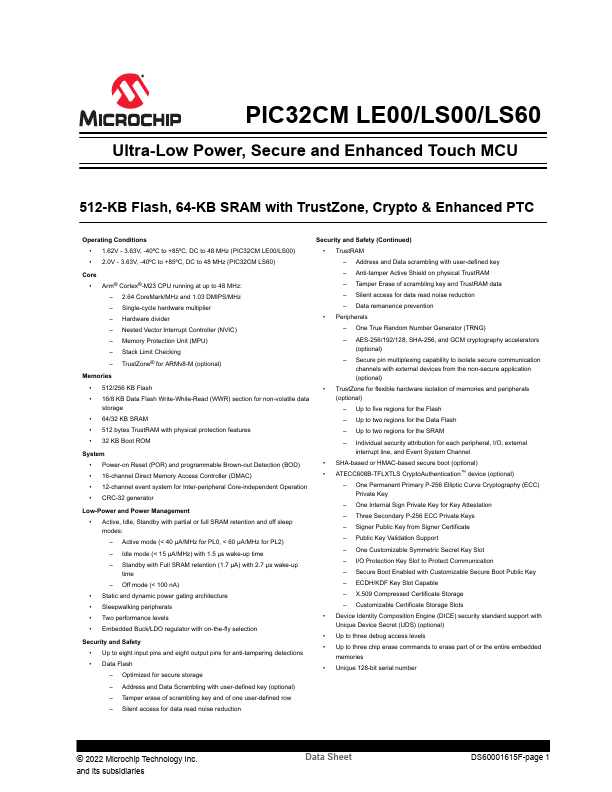

PIC32CMLS00 Overview

Key Features

- 32 KB Boot ROM System

- Power-on Reset (POR) and programmable Brown-out Detection (BOD)

- 16-channel Direct Memory Access Controller (DMAC)

- 12-channel event system for Inter-peripheral Core-independent Operation

- CRC-32 generator Low-Power and Power Management