Datasheet Summary

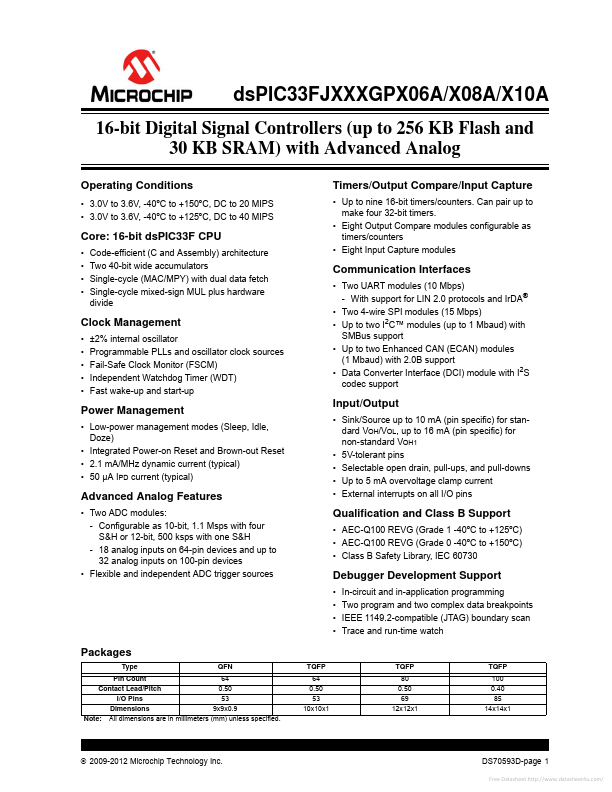

dsPIC33FJXXXGPX06A/X08A/X10A

16-bit Digital Signal Controllers (up to 256 KB Flash and 30 KB SRAM) with Advanced Analog

Operating Conditions

- 3.0V to 3.6V, -40ºC to +150ºC, DC to 20 MIPS

- 3.0V to 3.6V, -40ºC to +125ºC, DC to 40 MIPS

Timers/Output pare/Input Capture

- Up to nine 16-bit timers/counters. Can pair up to make four 32-bit timers.

- Eight Output pare modules configurable as timers/counters

- Eight Input Capture modules

Core: 16-bit dsPIC33F CPU

- -

- - Code-efficient (C and Assembly) architecture Two 40-bit wide accumulators Single-cycle (MAC/MPY) with dual data fetch Single-cycle mixed-sign MUL plus hardware divide munication Interfaces

- Two UART modules (10 Mbps)...