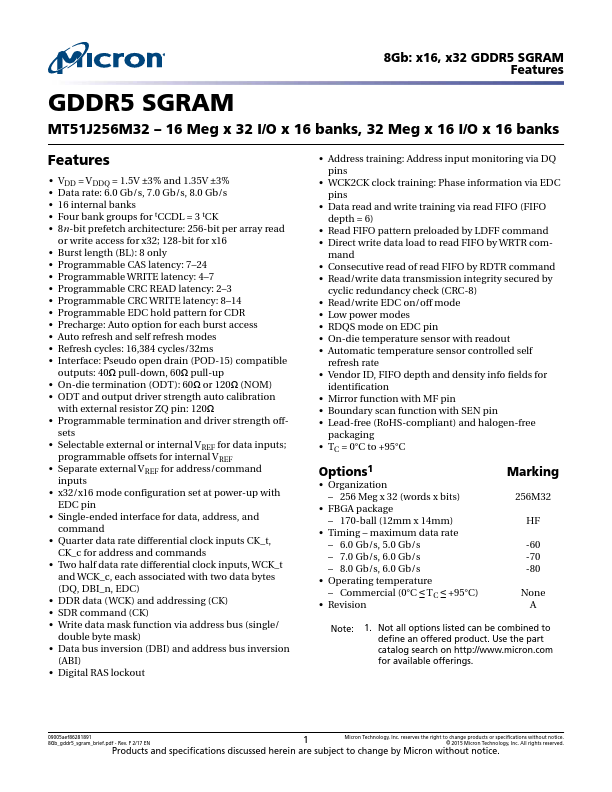

MT51J256M32 Overview

Key Features

- VDD = VDDQ = 1.5V ±3% and 1.35V ±3%

- Data rate: 6.0 Gb/s, 7.0 Gb/s, 8.0 Gb/s

- 16 internal banks

- Four bank groups for tCCDL = 3 tCK

- 8n-bit prefetch architecture: 256-bit per array read or write access for x32; 128-bit for x16

- Burst length (BL): 8 only

- Programmable CAS latency: 7–24

- Programmable WRITE latency: 4–7

- Programmable CRC READ latency: 2–3

- Programmable CRC WRITE latency: 8–14