MT5C128K8A1

MT5C128K8A1 is 128K x 8 SRAM manufactured by Micron Technology.

FEATURES

- High speed: 12, 15, 20 and 25ns

- Multiple center power and ground pins for greater noise immunity

- Easy memory expansion with ?C/E and ?O/E options

- Automatic ?C/E power down

- All inputs and outputs are TTL-patible

- High-performance, low-power, CMOS double-metal process

- Single +5V ± 10% power supply

- Fast ?O/E access times: 6, 8, 10 and 12ns

128K x 8 SRAM

WITH SINGLE CHIP ENABLE, REVOLUTIONARY PINOUT

5V ASYNCHRONOUS SRAM

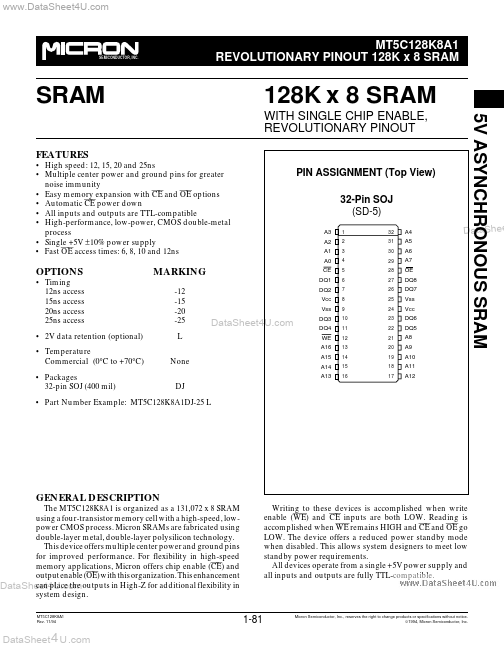

PIN ASSIGNMENT (Top View) 32-Pin SOJ (SD-5)

A3 A2 A1 A0 CE DQ1 DQ2 Vcc Vss DQ3 DQ4 WE A16 A15 A14 A13 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 A4 A5 A6 A7 OE DQ8 DQ7 Vss Vcc DQ6 DQ5 A8 A9 A10 A11 A12

Data Shee

OPTIONS

- Timing 12ns access 15ns access 20ns access 25ns access

- 2V data retention (optional)

- Temperature mercial (0°C to +70°C)

- Packages 32-pin SOJ (400 mil)

MARKING

-12 -15 -20 -25 L None DJ

.

- Part Number Example: MT5C128K8A1DJ-25 L

GENERAL DESCRIPTION

The MT5C128K8A1 is organized as a 131,072 x 8 SRAM using a four-transistor memory cell with a high-speed, lowpower CMOS process. Micron SRAMs are fabricated using double-layer metal, double-layer polysilicon technology. This device offers multiple center power and ground pins for improved performance. For flexibility in high-speed memory applications, Micron offers chip enable (?C/E) and output enable (?OE / ) with this organization. This enhancement can place the outputs in High-Z for additional flexibility in . system design.

MT5C128K8A1 Rev. 11/94

Writing to these devices is acplished when write enable (?W/E) and ?C/E inputs are both LOW. Reading is acplished when ?W/E remains HIGH and ?C/E and ?O/E go LOW. The device offers a reduced power standby mode when disabled. This allows system designers to meet low standby power requirements. All devices operate from a single +5V power supply and all inputs and outputs are fully TTL-patible.

1-81

Micron Semiconductor, Inc., reserves the right to change products or...