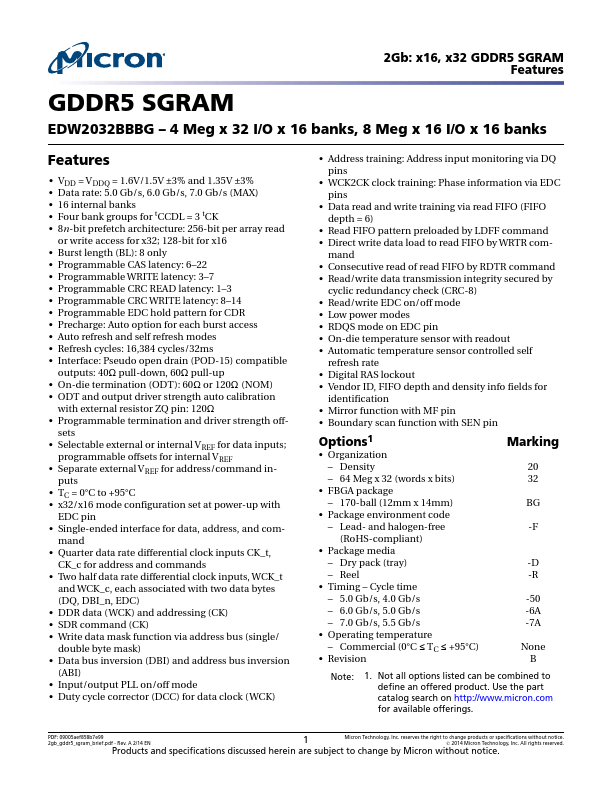

EDW2032BBBG

EDW2032BBBG is GDDR5 SGRAM manufactured by Micron Technology.

Features

GDDR5 SGRAM

- 4 Meg x 32 I/O x 16 banks, 8 Meg x 16 I/O x 16 banks

Features

- VDD = VDDQ = 1.6V/1.5V ±3% and 1.35V ±3%

- Data rate: 5.0 Gb/s, 6.0 Gb/s, 7.0 Gb/s (MAX)

- 16 internal banks

- Four bank groups for t CCDL = 3 t CK

- 8n-bit prefetch architecture: 256-bit per array read or write access for x32; 128-bit for x16

- Burst length (BL): 8 only

- Programmable CAS latency: 6- 22

- Programmable WRITE latency: 3- 7

- Programmable CRC READ latency: 1- 3

- Programmable CRC WRITE latency: 8- 14

- Programmable EDC hold pattern for CDR

- Precharge: Auto option for each burst access

- Auto refresh and self refresh modes

- Refresh cycles: 16,384 cycles/32ms

- Interface: Pseudo open drain (POD-15) patible outputs: 40Ω pull-down, 60Ω pull-up

- On-die termination (ODT): 60Ω or 120Ω (NOM)

- ODT and output driver strength auto calibration with external resistor ZQ pin: 120Ω

- Programmable termination and driver strength off- sets

- Selectable external or internal VREF for data inputs; programmable offsets for internal VREF

- Separate external VREF for address/mand in- puts

- TC = 0°C to +95°C

- x32/x16 mode configuration set at power-up with

EDC pin

- Single-ended interface for data, address, and

- mand

- Quarter data rate differential clock inputs CK_t,

CK_c for address and mands

- Two half data rate differential clock inputs, WCK_t and WCK_c, each associated with two data bytes (DQ, DBI_n, EDC)

- DDR data (WCK) and addressing (CK)

- SDR mand (CK)

- Write data mask function via address bus (single/ double byte mask)

- Data bus inversion (DBI) and address bus inversion (ABI)

- Input/output PLL on/off mode

- Duty cycle corrector (DCC) for data clock (WCK)

- Address training: Address input monitoring via DQ pins

- WCK2CK clock training: Phase information via EDC...