MT53E128M16D1

MT53E128M16D1 is LPDDR4/LPDDR4X SDRAM manufactured by Micron Technology.

Features

LPDDR4/LPDDR4X SDRAM

MT53E128M16D1, MT53E128M32D2

Features

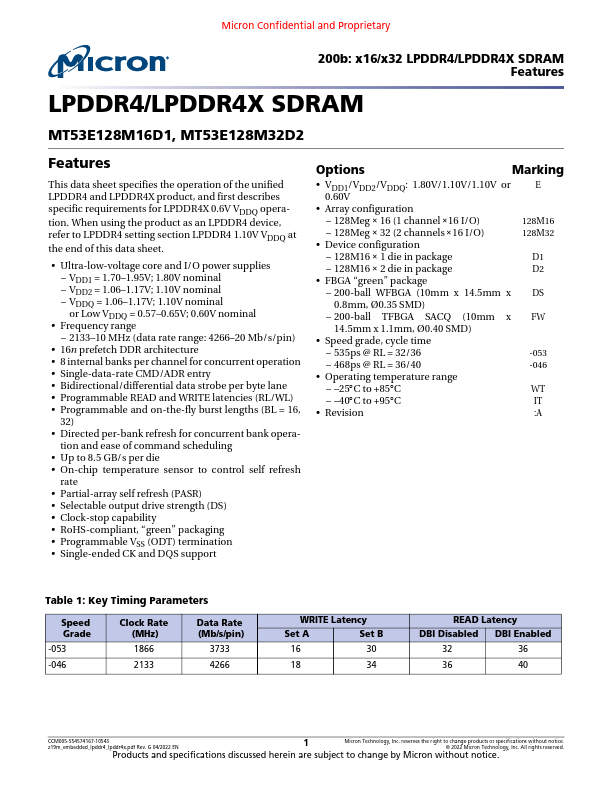

This data sheet specifies the operation of the unified LPDDR4 and LPDDR4X product, and first describes specific requirements for LPDDR4X 0.6V VDDQ operation. When using the product as an LPDDR4 device, refer to LPDDR4 setting section LPDDR4 1.10V VDDQ at the end of this data sheet.

- Ultra-low-voltage core and I/O power supplies

- VDD1 = 1.70- 1.95V; 1.80V nominal

- VDD2 = 1.06- 1.17V; 1.10V nominal

- VDDQ = 1.06- 1.17V; 1.10V nominal or Low VDDQ = 0.57- 0.65V; 0.60V nominal

- Frequency range

- 2133- 10 MHz (data rate range: 4266- 20 Mb/s/pin)

- 16n prefetch DDR architecture

- 8 internal banks per channel for concurrent operation

- Single-data-rate CMD/ADR entry

- Bidirectional/differential data strobe per byte lane

- Programmable READ and WRITE latencies (RL/WL)

- Programmable and on-the-fly burst lengths (BL = 16,

32)

- Directed per-bank refresh for concurrent bank opera- tion and ease of mand scheduling

- Up to 8.5 GB/s per die

- On-chip temperature sensor to control self refresh rate

- Partial-array self refresh (PASR)

- Selectable output drive strength (DS)

- Clock-stop capability

- Ro HS-pliant, “green” packaging

- Programmable VSS (ODT) termination

- Single-ended CK and DQS support

Options

Marking

- VDD1/VDD2/VDDQ: 1.80V/1.10V/1.10V or 0.60V

- Array configuration

- 128Meg × 16 (1 channel ×16 I/O)

- 128Meg × 32 (2 channels ×16 I/O)

- Device configuration

- 128M16 × 1 die in package

- 128M16 × 2 die in package

- FBGA “green” package

- 200-ball WFBGA (10mm x 14.5mm x 0.8mm, Ø0.35 SMD)

- 200-ball TFBGA SACQ (10mm x 14.5mm x 1.1mm, Ø0.40 SMD)

- Speed grade, cycle...