ZL30245

ZL30245 is Dual-Channel Any-to-Any Clock Multiplier and Frequency Synthesizer manufactured by Microsemi.

- Part of the ZL30244 comparator family.

- Part of the ZL30244 comparator family.

Features

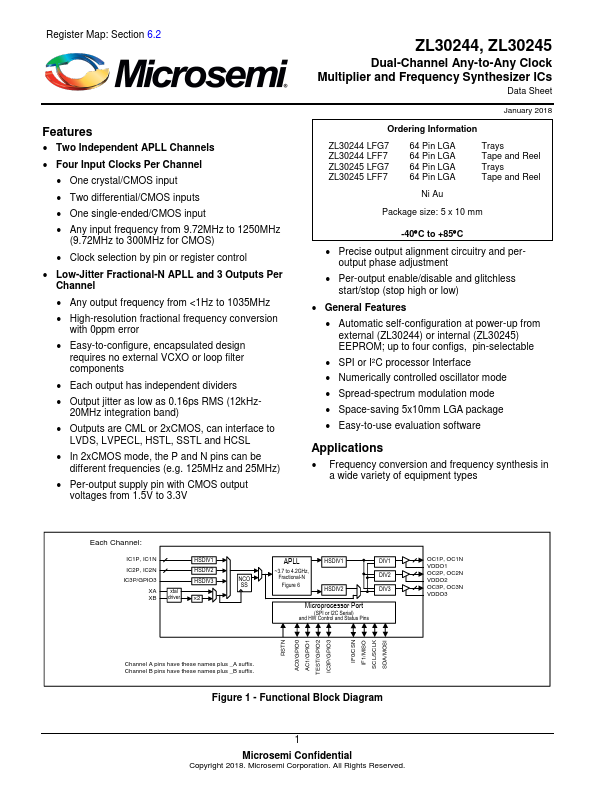

- Two Independent APLL Channels

- Four Input Clocks Per Channel

- One crystal/CMOS input

- Two differential/CMOS inputs

- One single-ended/CMOS input

- Any input frequency from 9.72MHz to 1250MHz

(9.72MHz to 300MHz for CMOS)

- Clock selection by pin or register control

- Low-Jitter Fractional-N APLL and 3 Outputs Per Channel

- Any output frequency from <1Hz to 1035MHz

- High-resolution fractional frequency conversion with 0ppm error

- Easy-to-configure, encapsulated design requires no external VCXO or loop filter ponents

- Each output has independent dividers

- Output jitter as low as 0.16ps RMS (12k Hz20MHz integration band)

- Outputs are CML or 2x CMOS, can interface to LVDS, LVPECL, HSTL, SSTL and HCSL

- In 2x CMOS mode, the P and N pins can be different frequencies (e.g. 125MHz and 25MHz)

- Per-output supply pin with CMOS output voltages from 1.5V to 3.3V

ZL30244, ZL30245

Dual-Channel Any-to-Any Clock Multiplier and Frequency Synthesizer ICs

Data Sheet

January 2018

Ordering Information

ZL30244 LFG7 ZL30244 LFF7 ZL30245 LFG7 ZL30245 LFF7

64 Pin LGA 64 Pin LGA 64 Pin LGA 64 Pin LGA

Trays Tape and Reel Trays Tape and Reel

Ni Au

Package size: 5 x 10 mm

-40C to +85C

- Precise output alignment circuitry and peroutput phase adjustment

- Per-output enable/disable and glitchless start/stop (stop high or low)

- General Features

- Automatic self-configuration at power-up from external (ZL30244) or internal (ZL30245) EEPROM; up to four configs, pin-selectable

- SPI or I2C processor Interface

- Numerically controlled oscillator mode

- Spread-spectrum modulation mode

- Space-saving 5x10mm LGA package

- Easy-to-use evaluation software

Applications

- Frequency conversion and frequency synthesis in a wide variety of equipment...