ZL40235

Overview

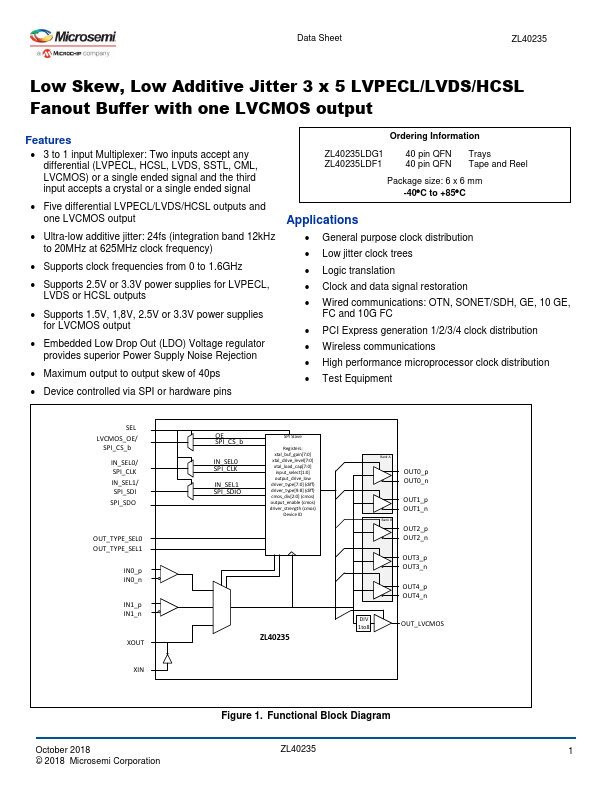

- 3 to 1 input Multiplexer: Two inputs accept any differential (LVPECL, HCSL, LVDS, SSTL, CML, LVCMOS) or a single ended signal and the third input accepts a crystal or a single ended signal

- Five differential LVPECL/LVDS/HCSL outputs and one LVCMOS output

- Ultra-low additive jitter: 24fs (integration band 12kHz to 20MHz at 625MHz clock frequency)

- Supports clock frequencies from 0 to 1.6GHz

- Supports 2.5V or 3.3V power supplies for LVPECL, LVDS or HCSL outputs

- Supports 1.5V, 1,8V, 2.5V or 3.3V power supplies for LVCMOS output

- Embedded Low Drop Out (LDO) Voltage regulator provides superior Power Supply Noise Rejection

- Maximum output to output skew of 40ps

- Device controlled via SPI or hardware pins