MT5C1001

MT5C1001 is 1M x 1 SRAM manufactured by Micross.

SRAM

MT5C1001 Limited Availability

1M x 1 SRAM

SRAM MEMORY ARRAY

AVAILABLE AS MILITARY SPECIFICATIONS

- SMD 5962-92316

- MIL-STD-883

Features

- High Speed: 20, 25, 35, and 45

- Battery Backup: 2V data retention

- Low power standby

- Single +5V (+10%) Power Supply

- Easy memory expansion with CE and OE options.

- All inputs and outputs are TTL patible

- Three-state output

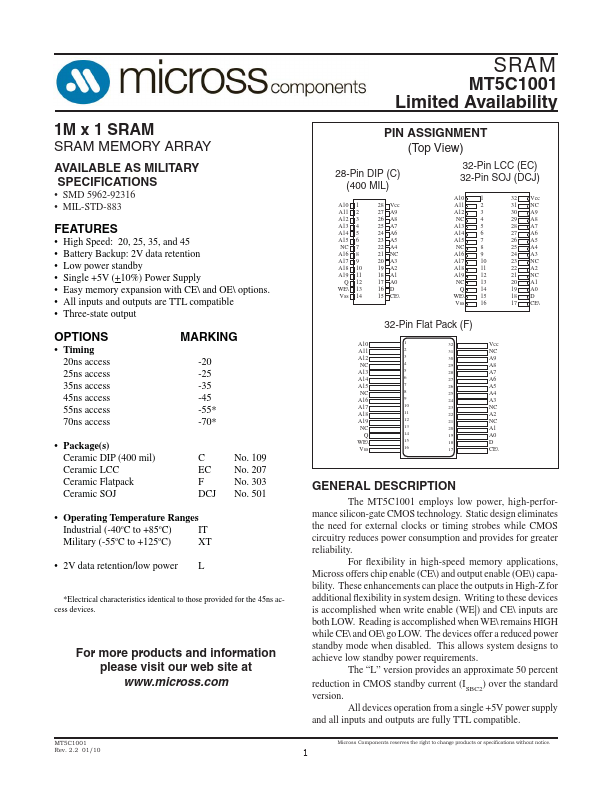

OPTIONS

- Timing 20ns access 25ns access 35ns access 45ns access 55ns access 70ns access

MARKING

-20 -25 -35 -45 -55- -70-

- Package(s) Ceramic DIP (400 mil) Ceramic LCC Ceramic Flatpack Ceramic SOJ

No. 109

EC No. 207

No. 303

DCJ No. 501

- Operating Temperature Ranges

Industrial (-40oC to...