MT9042

Overview

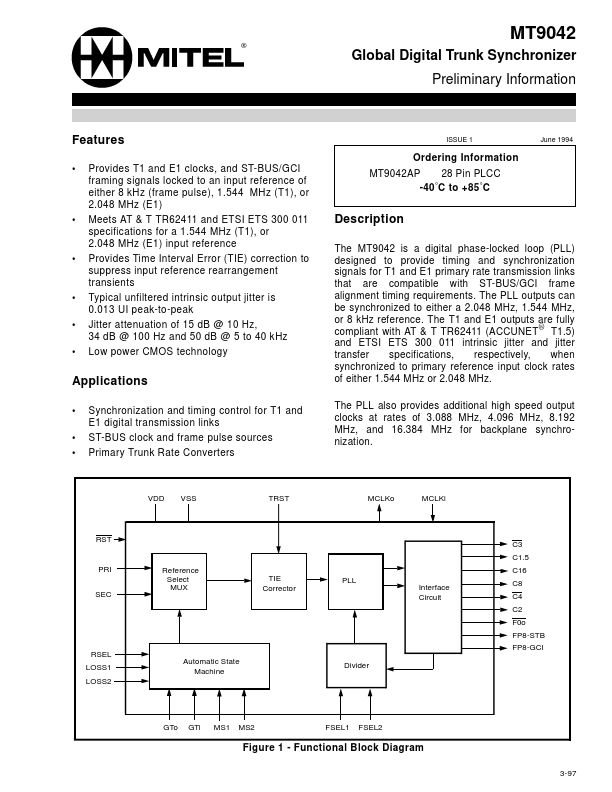

The MT9042 is a digital phase-locked loop (PLL) designed to provide timing and synchronization signals for T1 and E1 primary rate transmission links that are compatible with ST-BUS/GCI frame alignment timing requirements. The PLL outputs can be synchronized to either a 2.048 MHz, 1.544 MHz, or 8 kHz reference.

- Provides T1 and E1 clocks, and ST-BUS/GCI framing signals locked to an input reference of either 8 kHz (frame pulse), 1.544 MHz (T1), or 2.048 MHz (E1) Meets AT & T TR62411 and ETSI ETS 300 011 specifications for a 1.544 MHz (T1), or 2.048 MHz (E1) input reference Provides Time Interval Error (TIE) correction to suppress input reference rearrangement transients Typical unfiltered intrinsic output jitter is 0.013 UI peak-to-peak Jitter attenuation of 15 dB @ 10 Hz, 34 dB @ 100 Hz and 50 dB @ 5 to 40 kHz Low power CMOS technology ISSUE 1 June 1994