MT9074

MT9074 is T1/E1/J1 Single Chip Transceiver manufactured by Mitel Networks Corporation.

Features

- bined E1 (PCM 30) and T1 (D4/ESF) framer, Line Interface Unit (LIU) and link controller with optional digital framer only mode In T1 mode the LIU can recover signals attenuated by up to 36 d B (6000 ft. of 24 AWG cable) In E1 mode the LIU can recover signals attenuated by up to 36 d B (2000 m. of 0.65mm cable) Two HDLCs: FDL and channel 24 in T1 mode, timeslot 0 (Sa bits) and timeslot 16 in E1 mode Two-frame elastic buffer in Rx & Tx (T1) directions Programmable transmit delay through transmit slip buffer Low jitter DPLL for clock generation Enhanced alarms, performance monitoring and error insertion functions Intel or Motorola non-multiplexed parallel microprocessor interface ST-BUS 2.048 Mbit/s backplane bus for both data and signaling Japan Tele J1 Framing and Yellow Alarm Hardware data link access JTAG Boundary Scan

DS5024 ISSUE 5 September 1999

Ordering Information MT9074AP MT9074AL 68 Pin PLCC 100 Pin MQFP -40°C to 85°C

- -

- -

- -

- -

- -

- -

Description

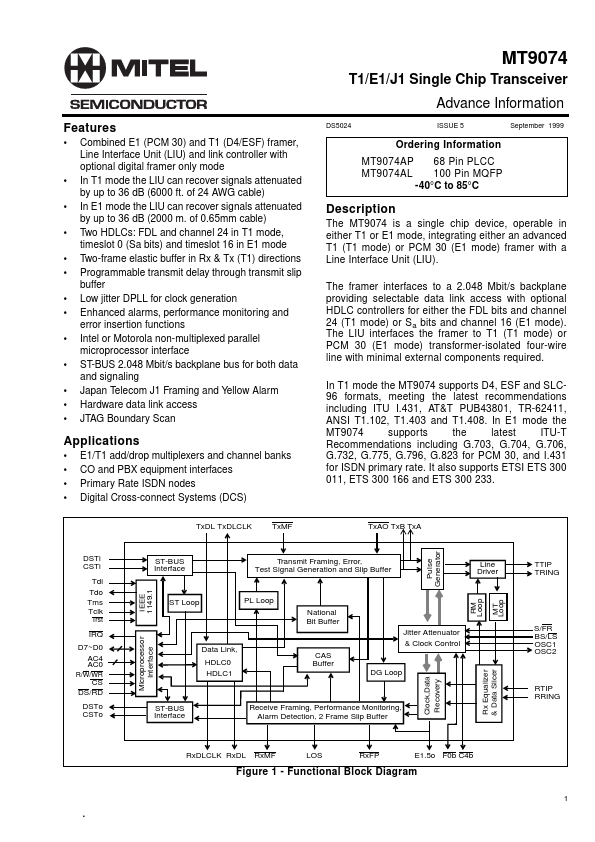

The MT9074 is a single chip device, operable in either T1 or E1 mode, integrating either an advanced T1 (T1 mode) or PCM 30 (E1 mode) framer with a Line Interface Unit (LIU). The framer interfaces to a 2.048 Mbit/s backplane providing selectable data link access with optional HDLC controllers for either the FDL bits and channel 24 (T1 mode) or Sa bits and channel 16 (E1 mode). The LIU interfaces the framer to T1 (T1 mode) or PCM 30 (E1 mode) transformer-isolated four-wire line with minimal external ponents required. In T1 mode the MT9074 supports D4, ESF and SLC96 formats, meeting the latest remendations including ITU I.431, AT&T PUB43801, TR-62411, ANSI T1.102, T1.403 and T1.408. In E1 mode the MT9074 supports the latest ITU-T Remendations including G.703, G.704, G.706, G.732, G.775, G.796, G.823 for PCM 30, and I.431 for ISDN primary rate. It also supports ETSI ETS 300 011, ETS 300 166 and ETS 300 233.

Applications

- -

- - E1/T1 add/drop multiplexers and channel banks CO and PBX equipment...