M5M44265CJ

M5M44265CJ is EDO (HYPER PAGE MODE) 4194304-BIT (262144-WORD BY 16-BIT) DYNAMIC RAM manufactured by Mitsubishi Electric.

- Part of the M5M comparator family.

- Part of the M5M comparator family.

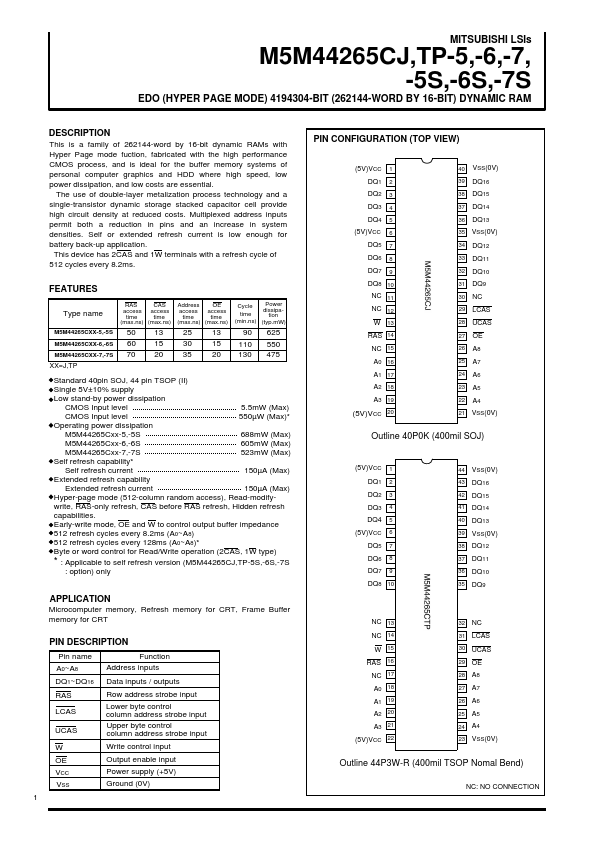

M5M44265CJ,TP-5,-6,-7, M5M44265CJ,TP-5,-6,-7,-5S,-6S,-7S -5S,-6S,-7S

EDO (HYPER PAGE MODE) 4194304-BIT (262144-WORD 16-BIT) DYNAMIC RAM EDO (HYPER PAGE MODE) 4194304-BIT (262144-WORD BY BY 16-BIT) DYNAMIC RAM

DESCRIPTION

This is a family of 262144-word by 16-bit dynamic RAMs with Hyper Page mode fuction, fabricated with the high performance CMOS process, and is ideal for the buffer memory systems of personal puter graphics and HDD where high speed, low power dissipation, and low costs are essential. The use of double-layer metalization process technology and a single-transistor dynamic storage stacked capacitor cell provide high circuit density at reduced costs. Multiplexed address...