M65667SP

M65667SP is PICTURE-IN-PICTURE SIGNAL PROCESSING manufactured by Mitsubishi Electric.

MITSUBISHI ICs (TV)

PRELIMINARY

Notice:This is not a final specification. Some parametric limits are subject to change.

PICTURE-IN-PICTURE SIGNAL PROCESSING

DESCRIPTION

The M65667SP is a NTSC PIP (Picture in Picture) signal processing LSI, whose sub and main-picture inputs are posite and Y/C separated signals, respectively. The built-in field memory (96k-bit RAM) ,V-chip data slicer and analog circuitries lead the PIP system low cost and small size.

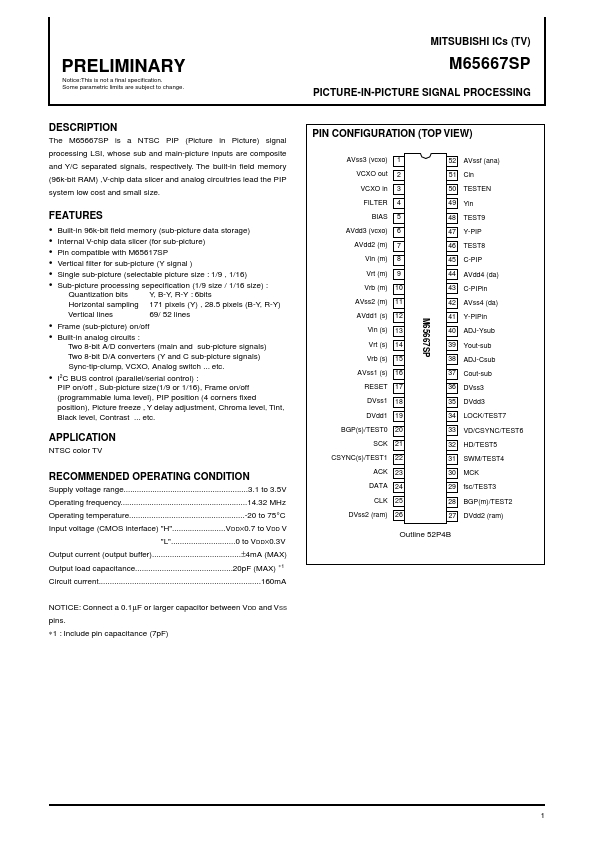

PIN CONFIGURATION (TOP VIEW)

AVss3 (vcxo) VCXO out VCXO in FILTER 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 52 AVssf (ana)

51 Cin 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 TESTEN Yin TEST9 Y-PIP TEST8 C-PIP AVdd4 (da) C-PIPin AVss4 (da) Y-PIPin ADJ-Ysub Yout-sub ADJ-Csub Cout-sub DVss3 DVdd3 LOCK/TEST7 VD/CSYNC/TEST6 HD/TEST5 SWM/TEST4 MCK fsc/TEST3 BGP(m)/TEST2 DVdd2 (ram)

Features

BIAS AVdd3 (vcxo) AVdd2 (m) Vin (m) Vrt (m) Vrb (m) AVss2 (m) AVdd1 (s) Vin (s) Vrt (s) Vrb (s) AVss1 (s) RESET DVss1 DVdd1 BGP(s)/TEST0

- -

- -

- -

Built-in 96k-bit field memory (sub-picture data storage) Internal V-chip data slicer (for sub-picture) Pin patible with M65617SP Vertical filter for sub-picture (Y signal ) Single sub-picture (selectable picture size : 1/9 , 1/16) Sub-picture processing sepecification (1/9 size / 1/16 size) : Quantization bits Y, B-Y, R-Y : 6bits Horizontal sampling 171 pixels (Y) , 28.5 pixels (B-Y, R-Y) Vertical lines 69/ 52 lines Frame (sub-picture) on/off Built-in analog circuits : Two 8-bit A/D converters (main and sub-picture signals) Two 8-bit D/A converters (Y and C sub-picture signals) Sync-tip-clump, VCXO, Analog switch ... etc. I2C BUS control (parallel/serial control) : PIP on/off , Sub-picture size(1/9 or 1/16), Frame on/off (programmable luma level), PIP position (4 corners fixed position), Picture freeze , Y delay adjustment, Chroma level, Tint, Black level, Contrast ... etc.

- -

- APPLICATION

NTSC color...