V58C3643204SAT

V58C3643204SAT is HIGH PERFORMANCE 3.3 VOLT 2M X 32 DDR SDRAM 4 X 512K X 32 manufactured by Mosel Vitelic Corp.

MOSEL VITELIC

V58C3643204SAT HIGH PERFORMANCE 3.3 VOLT 2M X 32 DDR SDRAM 4 X 512K X 32

PRELIMINARY

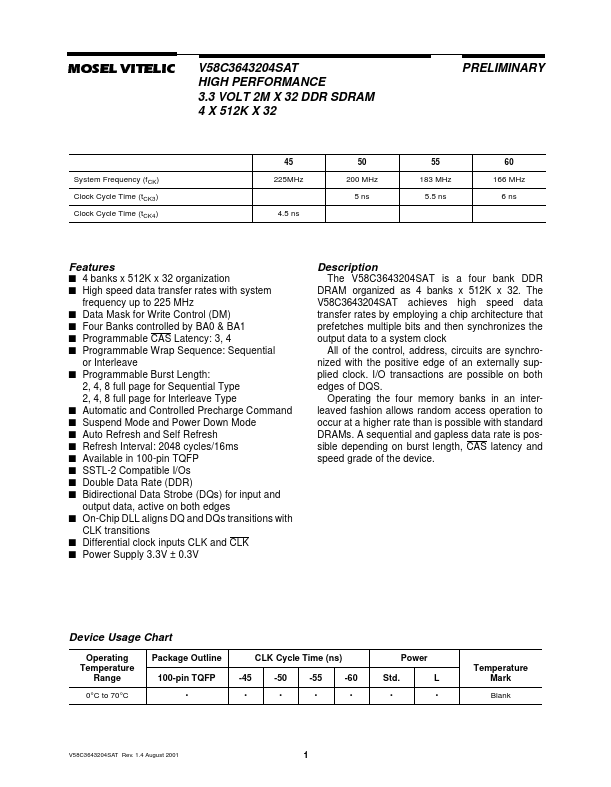

45 System Frequency (fCK) Clock Cycle Time (tCK3) Clock Cycle Time (tCK4) 4.5 ns 225MHz

50 200 MHz 5 ns

55 183 MHz 5.5 ns

60 166 MHz 6 ns

Features s 4 banks x 512K x 32 organization s High speed data transfer rates with system frequency up to 225 MHz s Data Mask for Write Control (DM) s Four Banks controlled by BA0 & BA1 s Programmable CAS Latency: 3, 4 s Programmable Wrap Sequence: Sequential or Interleave s Programmable Burst Length: 2, 4, 8 full page for Sequential Type 2, 4, 8 full page for Interleave Type s Automatic and Controlled Precharge mand s Suspend Mode and Power Down...