MPC958

MPC958 is LOW VOLTAGE PLL CLOCK DRIVER manufactured by Motorola Semiconductor.

MOTOROLA

Freescale Semiconductor, Inc.

SEMICONDUCTOR TECHNICAL DATA

Order this document by MPC958/D

Low Voltage PLL Clock Driver

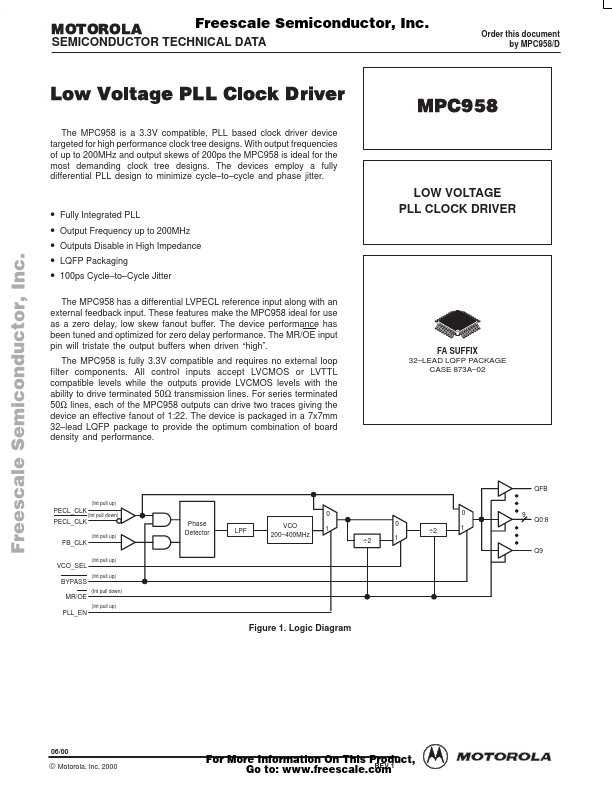

The MPC958 is a 3.3V patible, PLL based clock driver device targeted for high performance clock tree designs. With output frequencies of up to 200MHz and output skews of 200ps the MPC958 is ideal for the most demanding clock tree designs. The devices employ a fully differential PLL design to minimize cycle- to- cycle and phase jitter.

- Fully Integrated PLL

- Output Frequency up to 200MHz

LOW VOLTAGE PLL CLOCK DRIVER

Freescale Semiconductor, Inc...

- Outputs Disable in High Impedance

- LQFP Packaging

- 100ps Cycle- to- Cycle Jitter

The MPC958 has a...