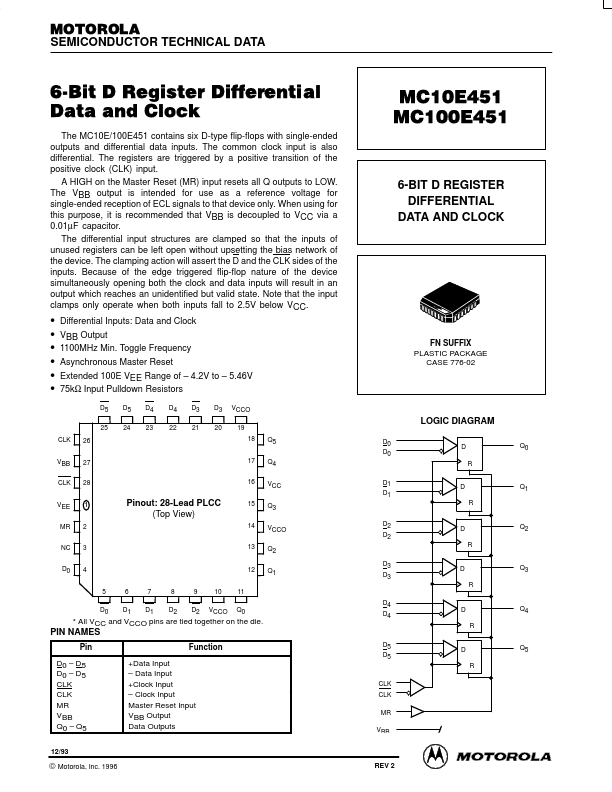

- Part: MC100E451

- Description: 6-BIT D REGISTER DIFFERENTIAL DATA AND CLOCK

- Manufacturer: Motorola Semiconductor

- Size: 112.58 KB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

| MC100E452 | onsemi | 5-BIT DIFFERENTIAL REGISTER |

| MC100E457 | onsemi | TRIPLE DIFFERENTIAL 2:1 MULTIPLEXER |