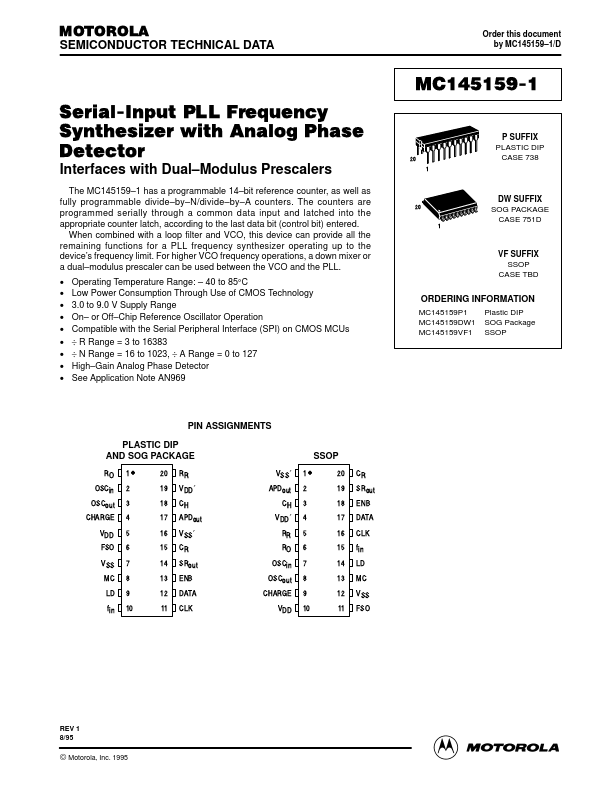

MC145159-1

MC145159-1 is Serial-Input PLL Frequency Synthesizer manufactured by Motorola Semiconductor.

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Serial-Input PLL Frequency Synthesizer with Analog Phase Detector

Interfaces with Dual- Modulus Prescalers

The MC145159- 1 has a programmable 14- bit reference counter, as well as fully programmable divide- by- N/divide- by- A counters. The counters are programmed serially through a mon data input and latched into the appropriate counter latch, according to the last data bit (control bit) entered.

When bined with a loop filter and VCO, this device can provide all the remaining functions for a PLL frequency synthesizer operating up to the device’s frequency limit. For higher VCO frequency operations, a down mixer or a dual- modulus prescaler can be used...