MCM6226BB

Key Features

- mount SOJ packages

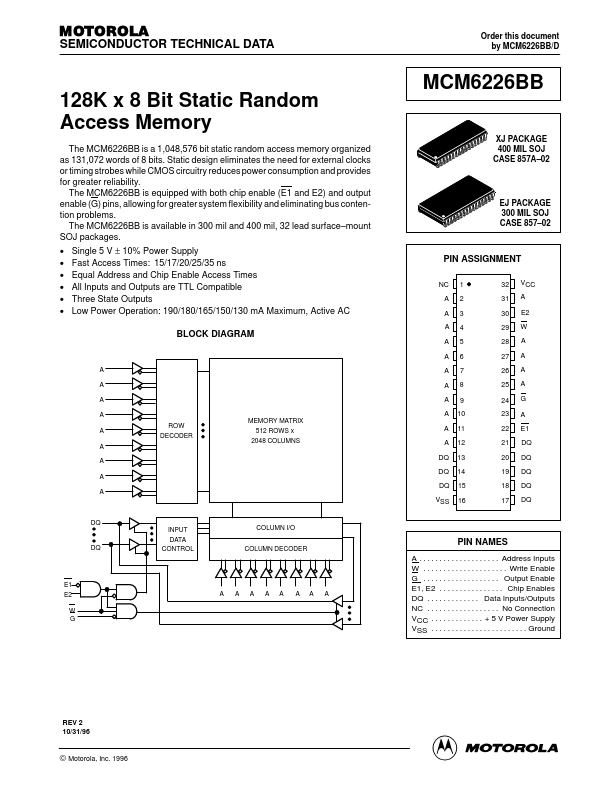

- Single 5 V ± 10% Power Supply Fast Access Times: 15/17/20/25/35 ns Equal Address and Chip Enable Access Times All Inputs and Outputs are TTL compatible Three State Outputs Low Power Operation: 190/180/165/150/130 mA Maximum, Active AC BLOCK DIAGRAM