MCM64PD32 Description

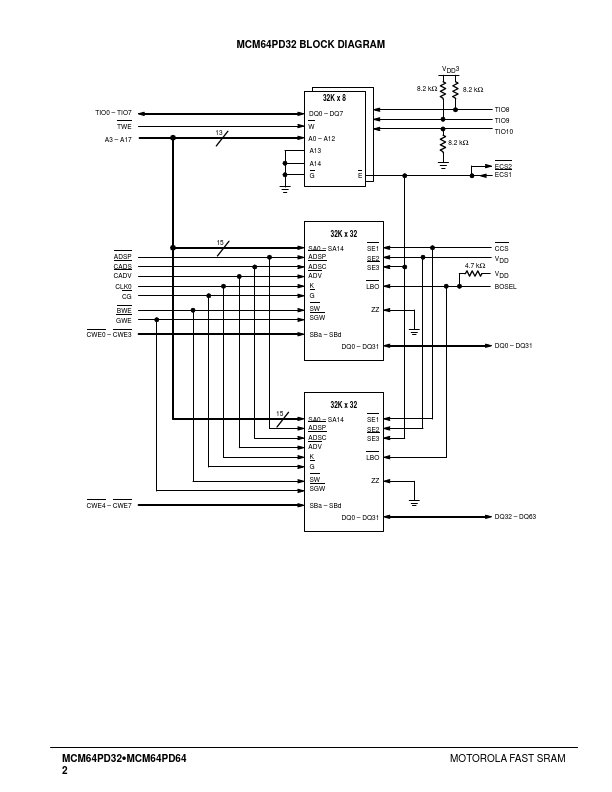

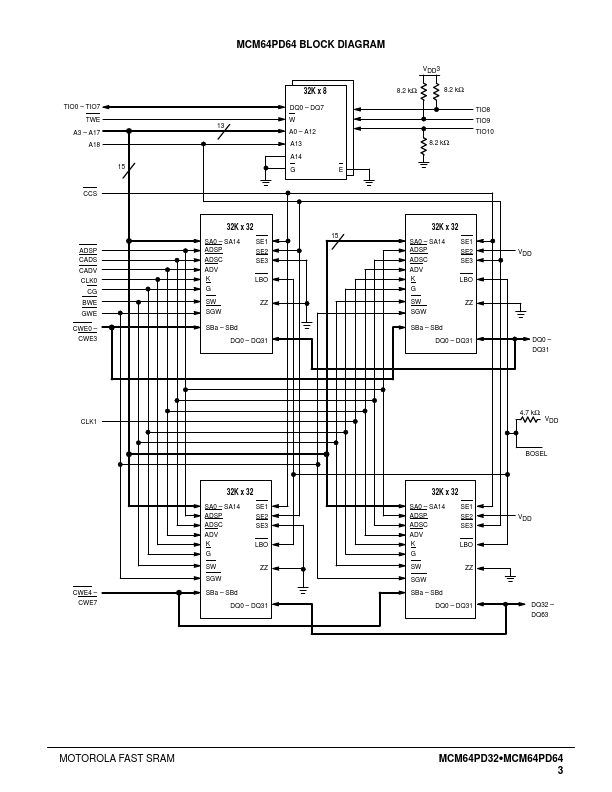

The MCM64PD32 is configured as 32K x 64 bits and the MCM64PD64 is configured as 64K x 64 bits. Both are packaged in a 160 pin card edge memory module. Each module uses Motorola’s 3.3 V 32K x 32 BurstRAMs and two Motorola 3.3 V 32K x 8 FSRAM for the tag RAM.