Datasheet Summary

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Order this document by MCM69P817/D

Product Preview

256K x 18 Bit Pipelined BurstRAM™ Synchronous Fast Static RAM

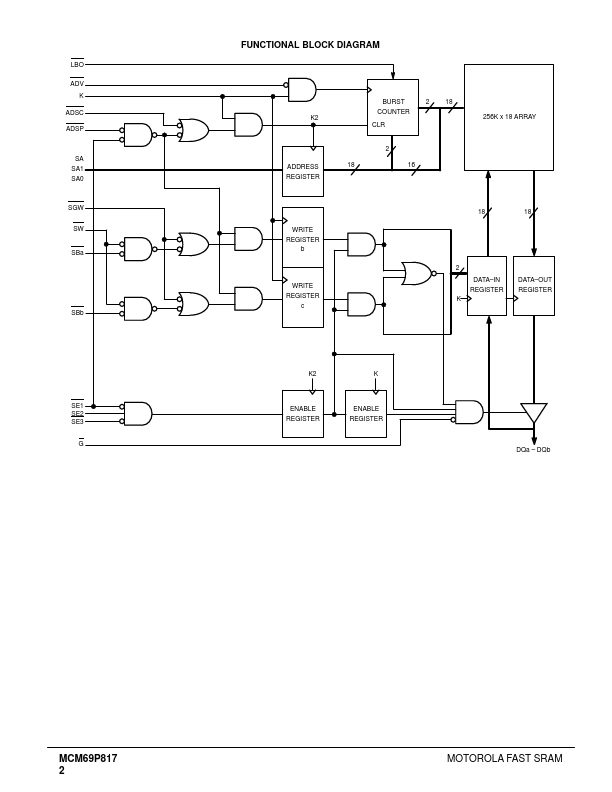

The MCM69P817 is a 4M bit synchronous fast static RAM designed to provide a burstable, high performance, secondary cache for the PowerPC™ and other high performance microprocessors. It is organized as 256K words of 18 bits each. This device integrates input registers, an output register, a 2- bit address counter, and a high speed SRAM onto a single monolithic circuit for reduced parts count in cache data RAM applications. Synchronous design allows precise cycle control with the use of an external clock (K). Addresses (SA), data...