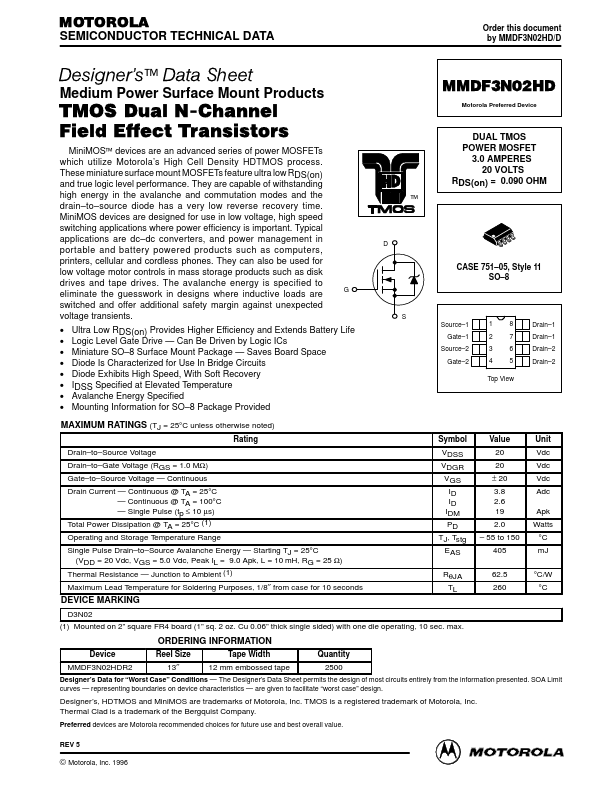

| Part | MMDF3N02HD |

|---|---|

| Description | Dual MOSFET |

| Category | MOSFET |

| Manufacturer | Motorola Semiconductor |

| Size | 297.98 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| MMDF3N02HD | onsemi | Power MOSFET |

| MMDF3N06VL | onsemi | Power MOSFET |

| MMDF3N04HD | onsemi | Power MOSFET |

| MMDF3N03HD | onsemi | Power MOSFET |