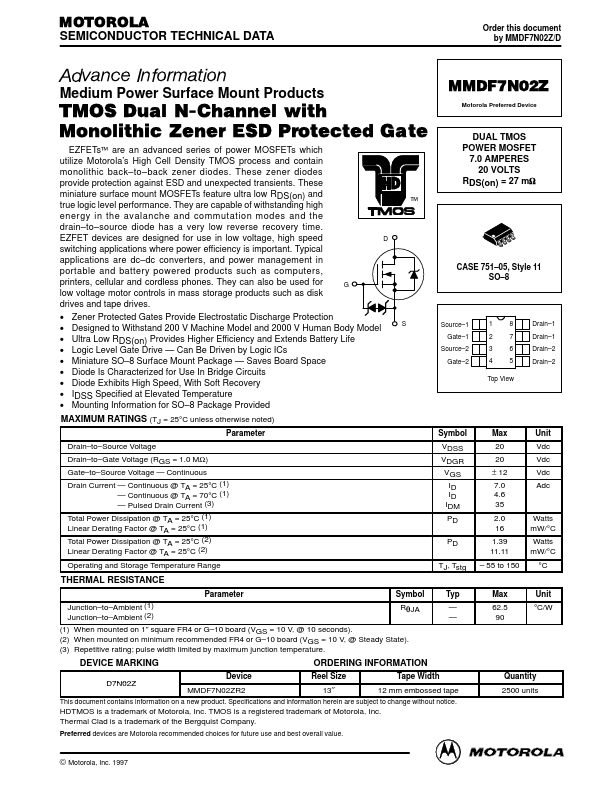

MMDF7N02Z Overview

Key Features

- Zener Protected Gates Provide Electrostatic Discharge Protection

- Designed to Withstand 200 V Machine Model and 2000 V Human Body Model

- Ultra Low RDS(on) Provides Higher Efficiency and Extends Battery Life

- Logic Level Gate Drive

- Can Be Driven by Logic ICs

- Miniature SO–8 Surface Mount Package

- Saves Board Space

- Diode Is Characterized for Use In Bridge Circuits

- Diode Exhibits High Speed, With Soft Recovery

- IDSS Specified at Elevated Temperature