Datasheet Summary

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Order this document by MPC2105A/D

512KB and 1MB BurstRAM™ Secondary Cache Modules for PowerPC™ PReP/CHRP Platforms

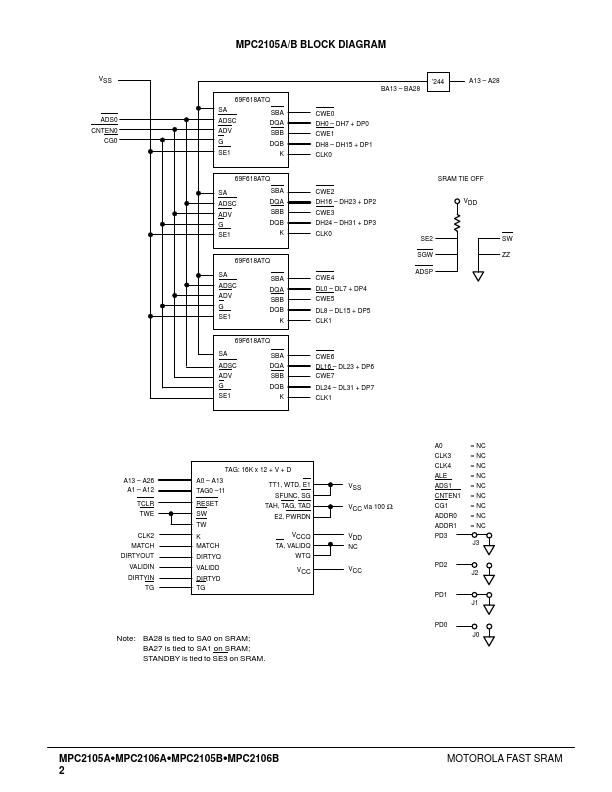

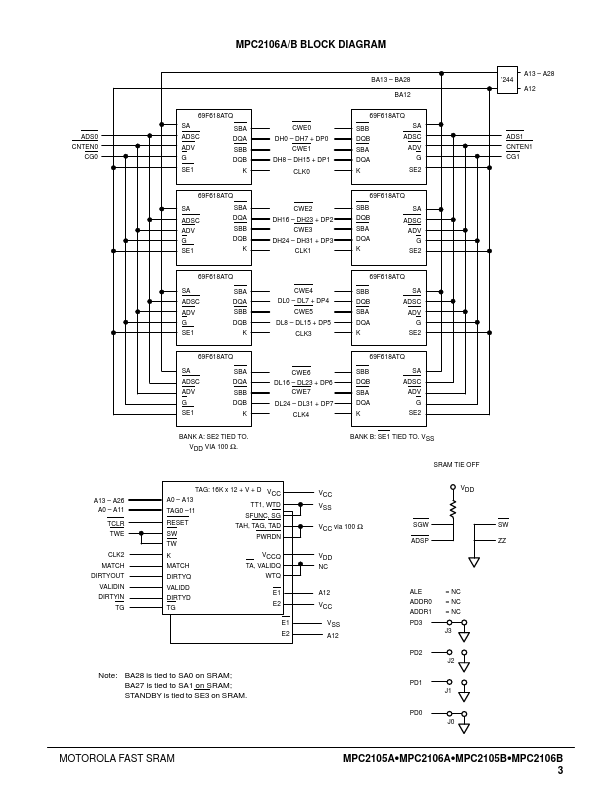

The MPC2105A/B and the MPC2106A/B are designed to provide burstable, high performance L2 cache for the PowerPC 60x microprocessor family in conformance with the PowerPC Reference Platform (PReP) and the PowerPC mon Hardware Reference Platform (CHRP) specifications. The MPC2105A/B and MPC2106A/B utilize synchronous BurstRAMs. The modules are configured as 64K x 72, and 128K x 72 bits in a 178 (89 x 2) pin DIMM format. The MPC2105A/B uses four of the 3 V 64K x 18; the MPC2106A/B uses eight of the 3 V 64K x 18. For tag bits, a 5 V cache...