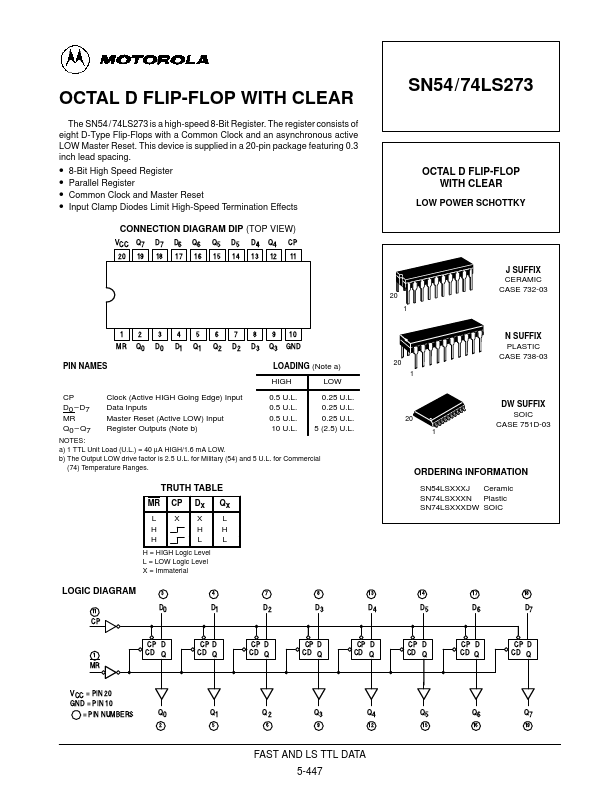

| Part | SN54LS273 |

|---|---|

| Description | OCTAL D FLIP-FLOP |

| Manufacturer | Motorola Semiconductor |

| Size | 183.89 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| SN54LS273 | Texas Instruments | OCTAL D-TYPE FLIP-FLOP |

| SN54LS27 | Texas Instruments | Triple 3-Input Positive-NOR Gates |

| SN54LS279A | Texas Instruments | QUADRUPLE S-R LATCHES |