SN74LS75 Overview

Key Specifications

Package: SOP

Mount Type: Surface Mount

Pins: 16

Operating Voltage: 5 V

Key Features

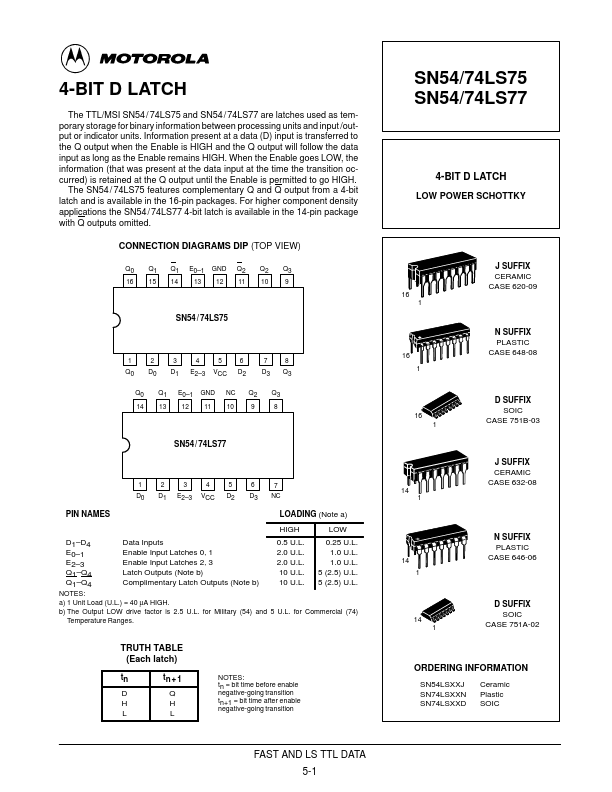

- complementary Q and Q output from a 4-bit latch and is available in the 16-pin packages

- For higher component density applications the SN54 / 74LS77 4-bit latch is available in the 14-pin package with Q outputs omitted

- 14 1 N SUFFIX PLASTIC CASE 646-06 NOTES: a) 1 Unit Load (U.L.) = 40 µA HIGH

- b) The Output LOW drive factor is 2.5 U.L

- for Military (54) and 5 U.L