CS5826 Overview

Description

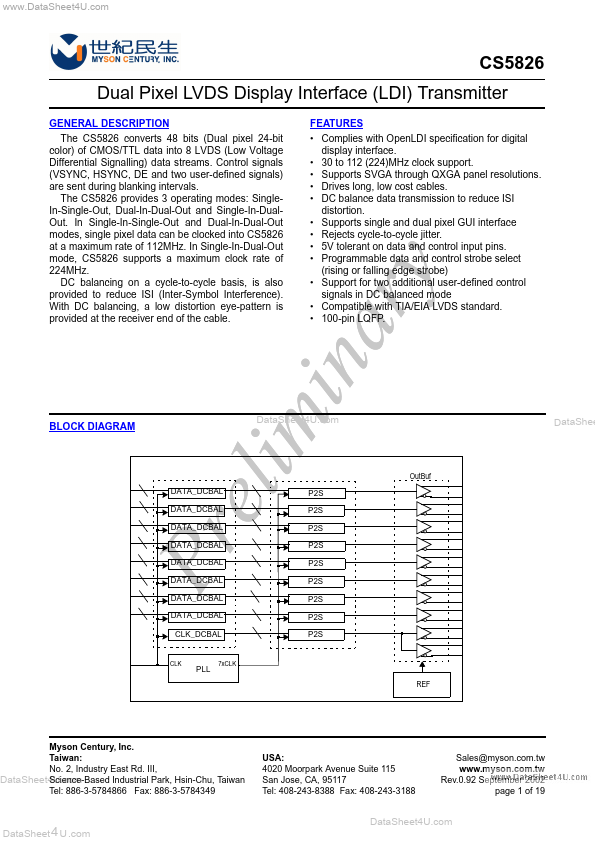

The CS5826 converts 48 bits (Dual pixel 24-bit color) of CMOS/TTL data into 8 LVDS (Low Voltage Differential Signalling) data streams. Control signals (VSYNC, HSYNC, DE and two user-defined signals) are sent during blanking intervals.

Key Features

- Complies with OpenLDI specification for digital display interface

- 30 to 112 (224)MHz clock support

- Supports SVGA through QXGA panel resolutions

- Drives long, low cost cables

- DC balance data transmission to reduce ISI distortion

- Supports single and dual pixel GUI interface

- Rejects cycle-to-cycle jitter

- 5V tolerant on data and control input pins

- Programmable data and control strobe select (rising or falling edge strobe)

- Support for two additional user-defined control signals in DC balanced mode