NT5SV4M16DT

NT5SV4M16DT is (NT5SVxxMxxDT) 64Mb Synchronous DRAM manufactured by NANYA.

- Part of the NT5SV16M4DT comparator family.

- Part of the NT5SV16M4DT comparator family.

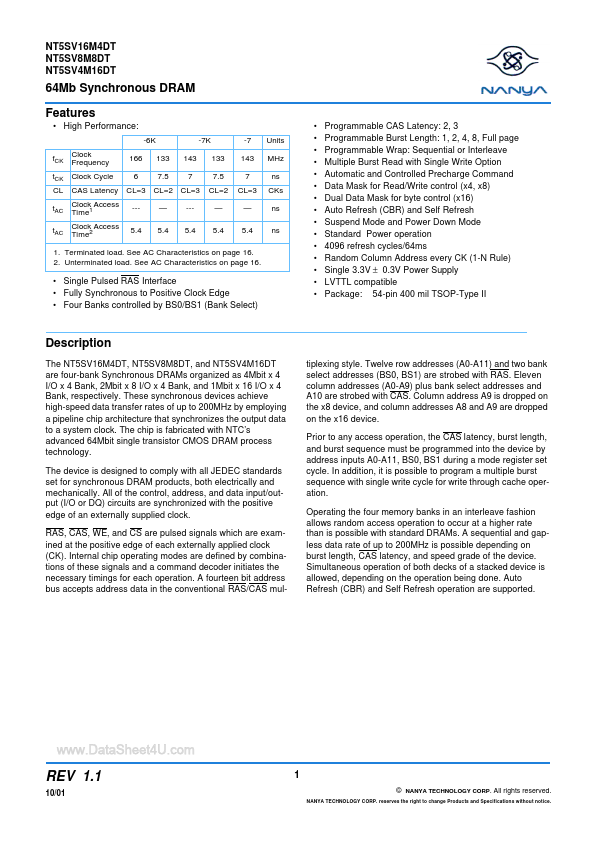

Features

- High Performance:

-6K f CK t CK CL t AC t AC Clock Frequency Clock Cycle CAS Latency Clock Access Time1 Clock Access Time2 166 6 133 7.5 143 7 -7K 133 7.5 CL=2

- 5.4 -7 143 7 CL=3

- 5.4 Units MHz ns CKs ns ns

CL=3 CL=2 CL=3 --5.4

- 5.4 --5.4

1. Terminated load. See AC Characteristics on page 16. 2. Unterminated load. See AC Characteristics on page 16.

- Single Pulsed RAS Interface

- Fully Synchronous to Positive Clock Edge

- Four Banks controlled by BS0/BS1 (Bank Select)

- -

- -

- -

- -

- -

- -

- -

- Programmable CAS Latency: 2, 3 Programmable Burst Length: 1, 2, 4, 8, Full page Programmable Wrap: Sequential or Interleave Multiple Burst Read with Single Write Option Automatic and Controlled Precharge mand Data Mask for Read/Write control (x4, x8) Dual Data Mask for byte control (x16) Auto Refresh (CBR) and Self Refresh Suspend Mode and Power Down Mode Standard Power operation 4096 refresh cycles/64ms Random Column Address every CK (1-N Rule) Single 3.3V ± 0.3V Power Supply LVTTL patible Package: 54-pin 400 mil TSOP-Type II

Description

The NT5SV16M4DT, NT5SV8M8DT, and NT5SV4M16DT are four-bank Synchronous DRAMs organized as 4Mbit x 4 I/O x 4 Bank, 2Mbit x 8 I/O x 4 Bank, and 1Mbit x 16 I/O x 4 Bank, respectively. These synchronous devices achieve high-speed data transfer rates of up to 200MHz by employing a pipeline chip architecture that synchronizes the output data to a system clock. The chip is fabricated with NTC’ s advanced 64Mbit single transistor CMOS DRAM process technology. The device is designed to ply with all JEDEC standards set for synchronous DRAM products, both electrically and mechanically. All of the control, address, and data input/output (I/O or DQ) circuits are synchronized with the positive edge of an externally supplied clock. RAS, CAS, WE, and CS are pulsed signals which are examined at the positive edge of each externally applied clock (CK). Internal chip operating modes are defined by binations of these signals and a mand...