D4701A

D4701A is UPD4701A manufactured by NEC.

DATA SHEET

MOS INTEGRATED CIRCUIT

µPD4701A

INCREMENTAL ENCODER COUNTER

DESCRIPTION

The µPD4701A is a counter for an X, Y 2-axis incremental encoder. When a two-phase encoder signal is input for the X and Y axes, direction discrimination and putation is performed, and count data is output in 8-bit parallel form. In addition, a 3-contact-point input buffer is incorporated, which is useful for applications which use a pointing device such as a mouse or track-ball. The CPU checks the switch input flag or count flag and reads the 12-bit count data in two operations, one for the lower byte and one for the upper byte. The key input flag is output together with the count data in the upper byte.

Features

- X, Y 2-axis incremental encoder counter

- Counter input (Schmitt-triggered input) X axis: XA, XB 2-phase signal 4-multiplication count method used Y axis: YA, YB 2-phase signal

- Counters: 12-bit binary up/down counters (2 sets, X & Y) Reset value: 000H

- Count data output: 8-bit parallel latch output × 2 (including key input flag)

- On-chip 3-contact-point key input buffer circuit

- CMOS

- Single +5 V power supply

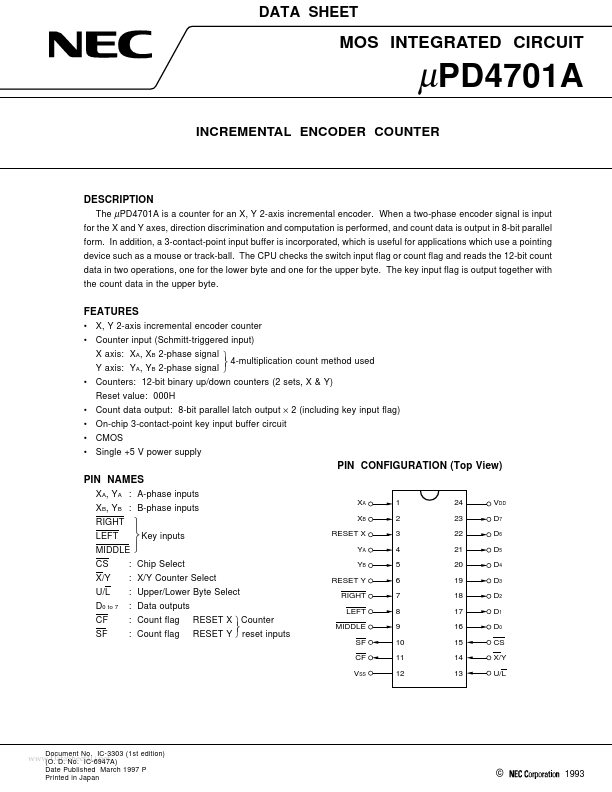

PIN CONFIGURATION (Top View) PIN NAMES

XA, YA : A-phase inputs XB, YB : B-phase inputs

XA XB RESET X YA YB RESET Y RIGHT LEFT 1 2 3 4 5 6 7 8 9 10 11 12 24 23 22 21 20 19 18 17 16 15 14 13 VDD D7 D6 D5 D4 D3 D2 D1 D0 CS X/Y U/L

LEFT Key inputs MIDDLE

RIGHT CS X/Y U/L D0 to 7 CF SF : Chip Select : X/Y Counter Select : Upper/Lower Byte Select : Data outputs : Count flag : Count flag RESET X Counter RESET Y reset inputs

MIDDLE SF CF VSS

..net (O. D. No. IC-6947A)

Document No. IC-3303 (1st edition) Date Published March 1997 P Printed in Japan

©

µPD4701A

ORDERING INFORMATION

Part Number Package 24-pin plastic DIP (600 mil) 24-pin plastic SOP (375 mil)

µPD4701AC µPD4701AGT

BLOCK DIAGRAM

XA XB

Phase Determination and Edge...