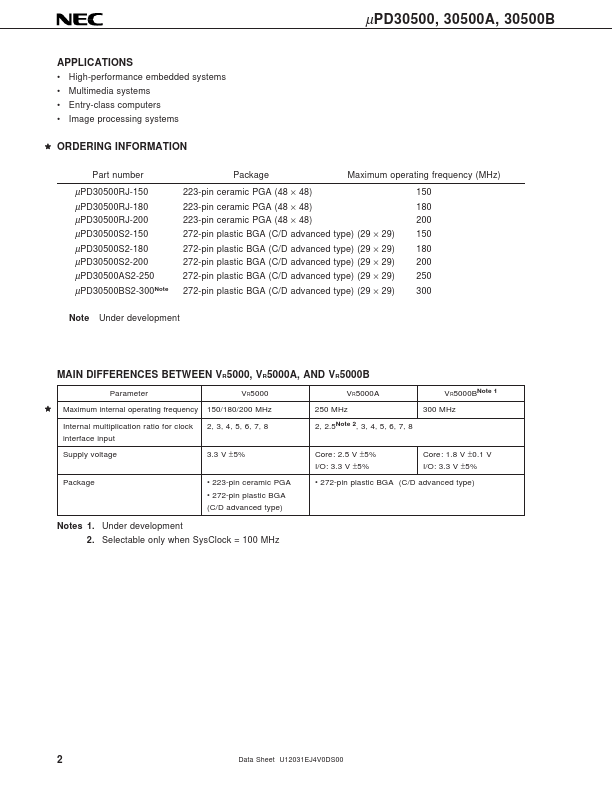

Datasheet Summary

DATA SHEET

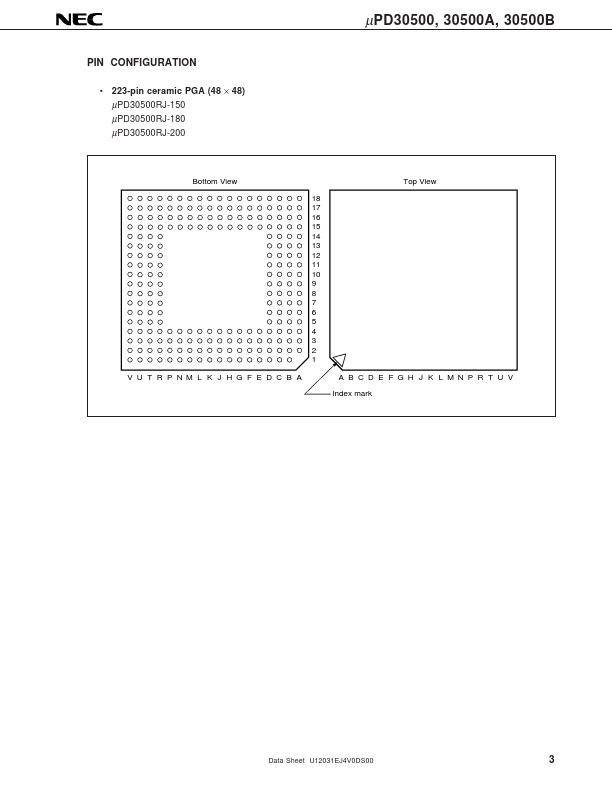

µPD30500, 30500A, 30500B

VR5000TM, VR5000ATM, VR5000BTM 64-BIT MICROPROCESSOR

MOS INTEGRATED CIRCUIT

DESCRIPTION

The µPD30500 (VR5000), µPD30500A (VR5000A), and µPD30500BNote (VR5000B) are a high-performance, 64bit RISC (Reduced Instruction Set puter) type microprocessors employing the RISC architecture developed by MIPSTM Technologies Inc. The instructions of the VR5000, VR5000A, and VR5000B are patible with those of the VR3000TM Series and VR4000TM Series and higher, and pletely patible with those of the VR10000TM. applications can be used as they are. Note Under development Therefore, present

Detailed functions are described in the following manual. Be sure to...