Datasheet Summary

NEe Microputers, Inc.

NEe p.PD4104 p.PD41 04- 1 pPD41 04- 2

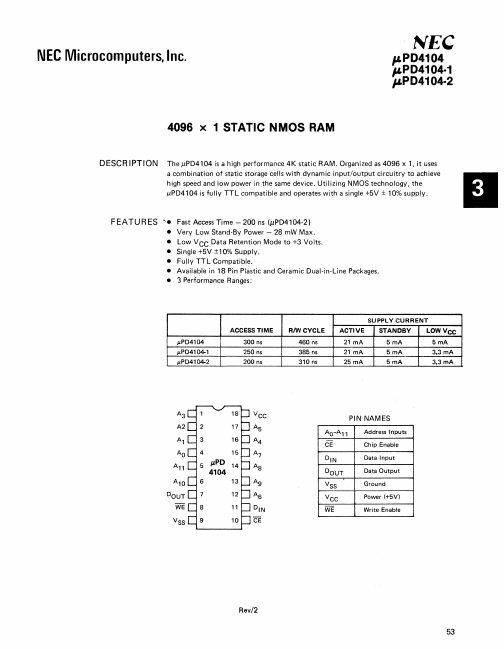

4096 x 1 STATIC NMOS RAM

DEseR IPTION

The J.LPD4104 is a high performance 4K static RAM. Organized as 4096 x 1, it uses a bination of static storage cells with dynamic input/output circuitry to achieve high speed and low power in the same device. Utilizing NMOS technology, the J.LPD4104 is fully TTL patible and operates with a single +5V ± 10% supply.

Features

' . FastAccessTime-200ns (J.LPD4104-2)

- Very Low Stand-By Power

- 28 mW Max.

- Low VCC Data Retention Mode to +3 Volts.

- Single +5V ±10% Supply.

- Fully TTL patible.

- Available in 18 Pin Plastic and Ceramic Dual-in-Line Packages.

- '3 Performance...