Datasheet Summary

..

DATA SHEET

MOS INTEGRATED CIRCUIT

µPD44323362

32M-BIT CMOS SYNCHRONOUS FAST STATIC RAM 1M-WORD BY 36-BIT HSTL INTERFACE / REGISTER-REGISTER / LATE WRITE

Description

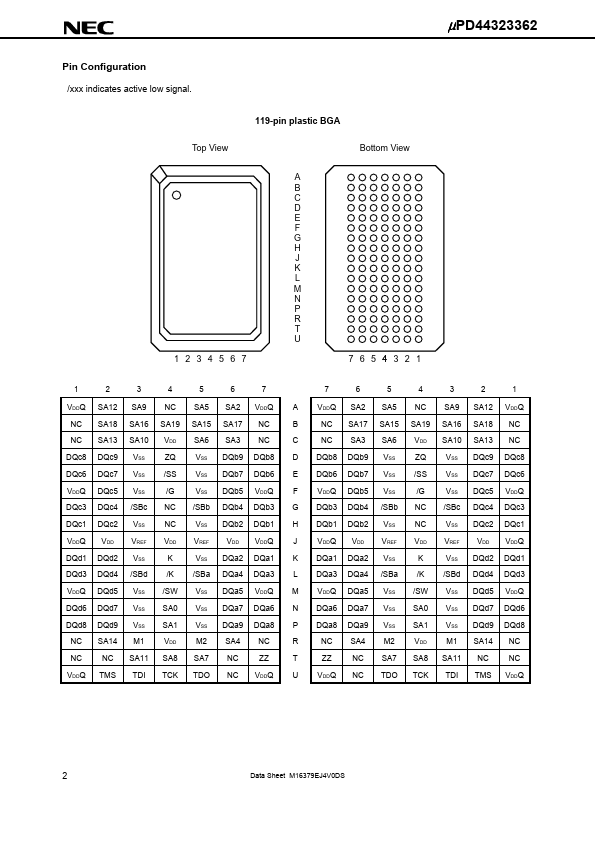

The µPD44323362 is a 1,048,576 words by 36 bits synchronous static RAM fabricated with advanced CMOS technology using Full-CMOS six-transistor memory cell. The µPD44323362 is suitable for applications which require high-speed, low voltage, high-density memory and wide bit configuration, such as cache and buffer memory. The µPD44323362 is packaged in a 119-pin PLASTIC BGA (Ball Grid Array).

Features

- Fully synchronous operation

- HSTL Input / Output levels

- Fast clock access time: 2.0 ns / 250 MHz

-...