Datasheet Summary

DATA SHEET

MOS INTEGRATED CIRCUIT

µPD720101

USB2.0 HOST CONTROLLER

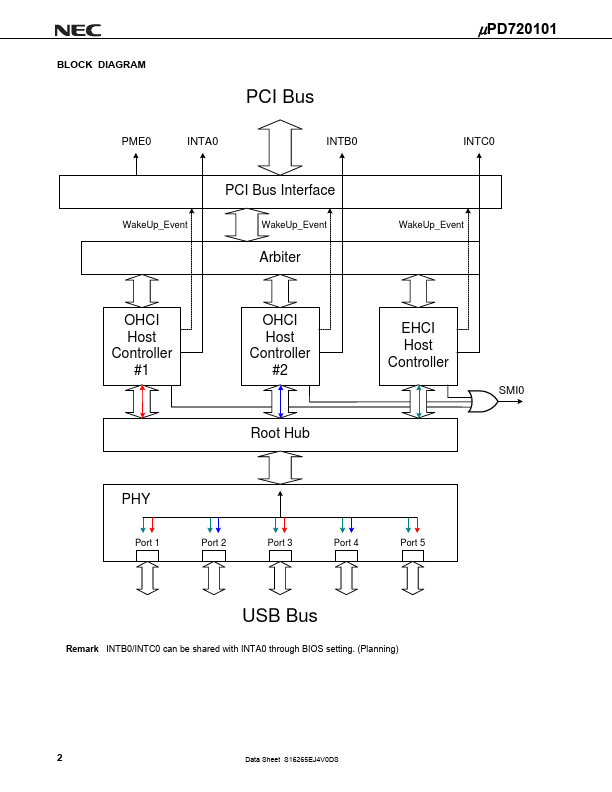

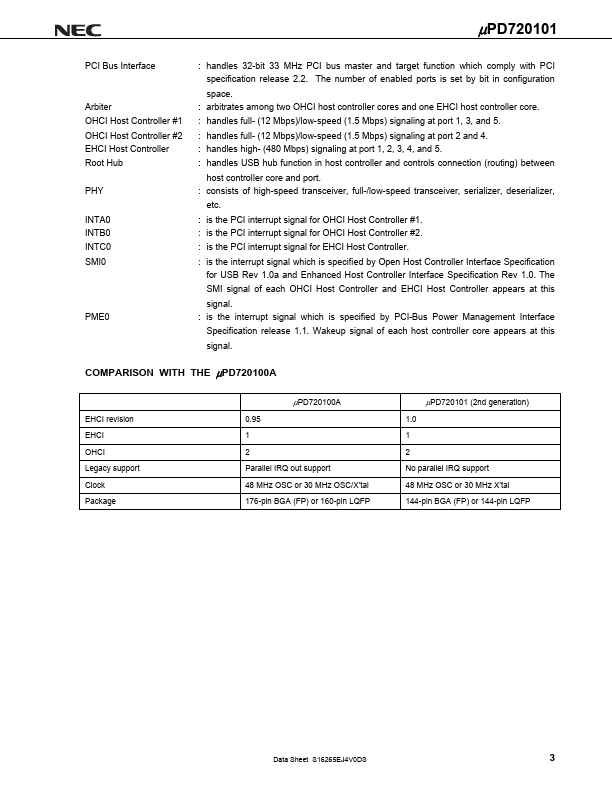

The µPD720101 plies with the Universal Serial Bus Specification Revision 2.0 and Open Host Controller Interface Specification for full-/low-speed signaling and Intel's Enhanced Host Controller Interface Specification for high-speed signaling and works up to 480 Mbps. The µPD720101 is integrated 3 host controller cores with PCI interface and USB2.0 transceivers into a single chip. Detailed function descriptions are provided in the following user’s manual. Be sure to read the manual before designing.

µPD720101 User’s Manual: S16336E

Features

- pliant with Universal Serial Bus Specification Revision 2.0 (Data rate...