UPD72871

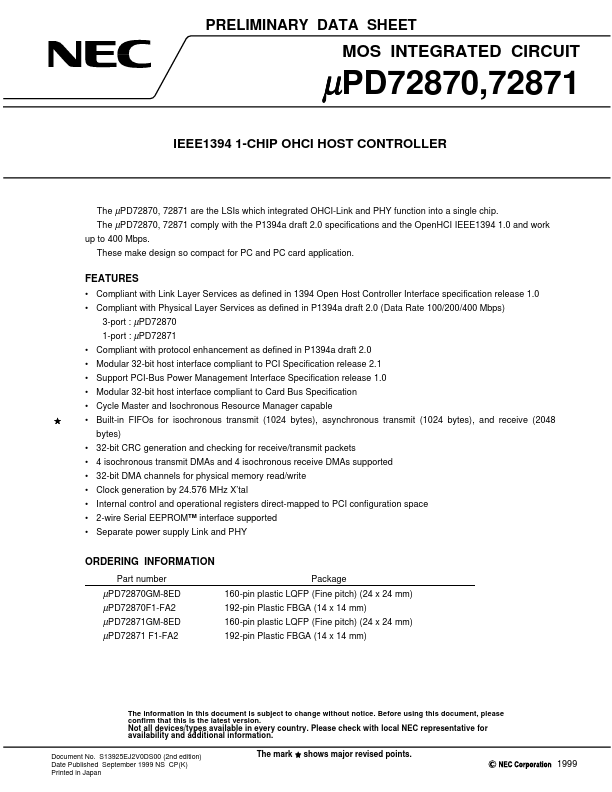

Overview

- Compliant with Link Layer Services as defined in 1394 Open Host Controller Interface specification release 1.0

- Compliant with Physical Layer Services as defined in P1394a draft 2.0 (Data Rate 100/200/400 Mbps) 3-port : µPD72870 1-port : µPD72871

- Compliant with protocol enhancement as defined in P1394a draft 2.0

- Modular 32-bit host interface compliant to PCI Specification release 2.1

- Support PCI-Bus Power Management Interface Specification release 1.0

- Modular 32-bit host interface compliant to Card Bus Specification

- Cycle Master and Isochronous Resource Manager capable 5

- Built-in FIFOs for isochronous transmit (1024 bytes), asynchronous transmit (1024 bytes), and receive (2048 bytes)

- 32-bit CRC generation and checking for receive/transmit packets

- 4 isochronous transmit DMAs and 4 isochronous receive DMAs supported