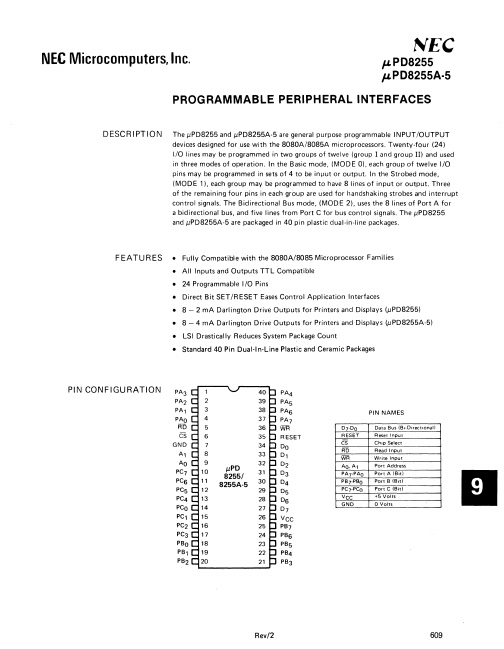

| Part | UPD8255A-5 |

|---|---|

| Description | PROGRAMMABLE PERIPHERAL INTERFACES |

| Manufacturer | NEC |

| Size | 374.28 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| AZ1515-04S | Amazing Microelectronic | Low Capacitance ESD Protection Array For High Speed Data Interfaces |

| CDP1882 | Intersil | CMOS 6-Bit Latch and Decoder Memory Interfaces |

| CDP1883 | Intersil | CMOS 7-Bit Latch and Decoder Memory Interfaces |