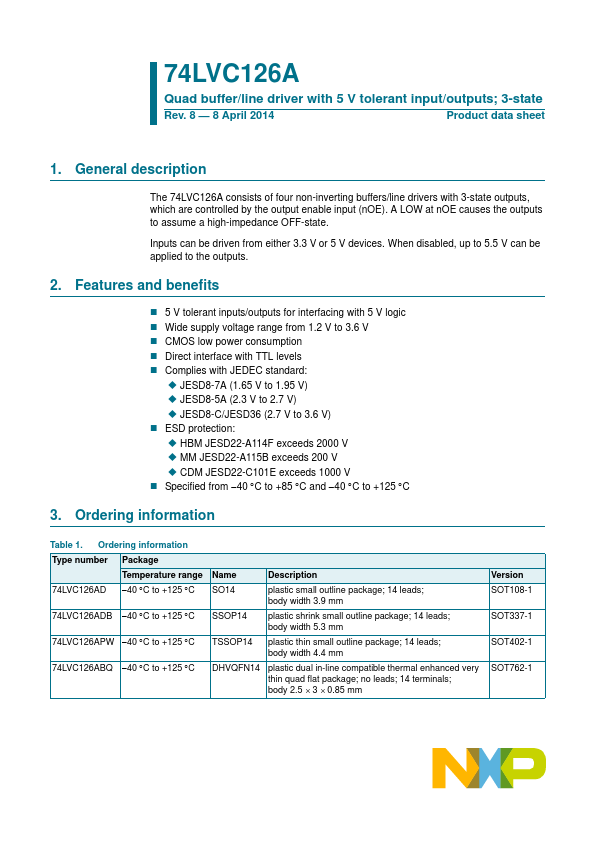

74LVC126A

Overview

The 74LVC126A consists of four non-inverting buffers/line drivers with 3-state outputs, which are controlled by the output enable input (nOE). A LOW at nOE causes the outputs to assume a high-impedance OFF-state.

- 5 V tolerant inputs/outputs for interfacing with 5 V logic

- Wide supply voltage range from 1.2 V to 3.6 V

- CMOS low power consumption

- Direct interface with TTL levels

- Complies with JEDEC standard:; JESD8-7A (1.65 V to 1.95 V); JESD8-5A (2.3 V to 2.7 V); JESD8-C/JESD36 (2.7 V to 3.6 V)

- ESD protection:; HBM JESD22-A114F exceeds 2000 V; MM JESD22-A115B exceeds 200 V; CDM JESD22-C101E exceeds 1000 V

- Specified from -40 °C to +85 °C and -40 °C to +12