DSP56652

DSP56652 is INTEGRATED CELLULAR BASEBAND PROCESSOR manufactured by NXP Semiconductors.

MOTOROLA Freescale Semiconductor, Inc.

SEMICONDUCTOR TECHNICAL DATA

Order this document by: DSP56652/D Rev 1, 1/99

Advance Information

INTEGRATED CELLULAR BASEBAND PROCESSOR

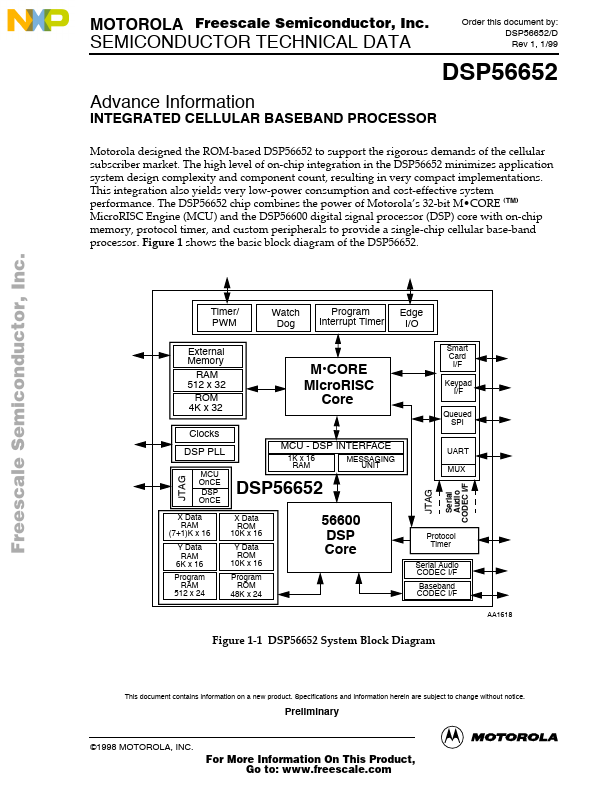

Motorola designed the ROM-based DSP56652 to support the rigorous demands of the cellular subscriber market. The high level of on-chip integration in the DSP56652 minimizes application system design plexity and ponent count, resulting in very pact implementations. This integration also yields very low-power consumption and cost-effective system performance. The DSP56652 chip bines the power of MotorolaÕs 32-bit M- CORE (TM) MicroRISC Engine (MCU) and the DSP56600 digital signal processor (DSP)...