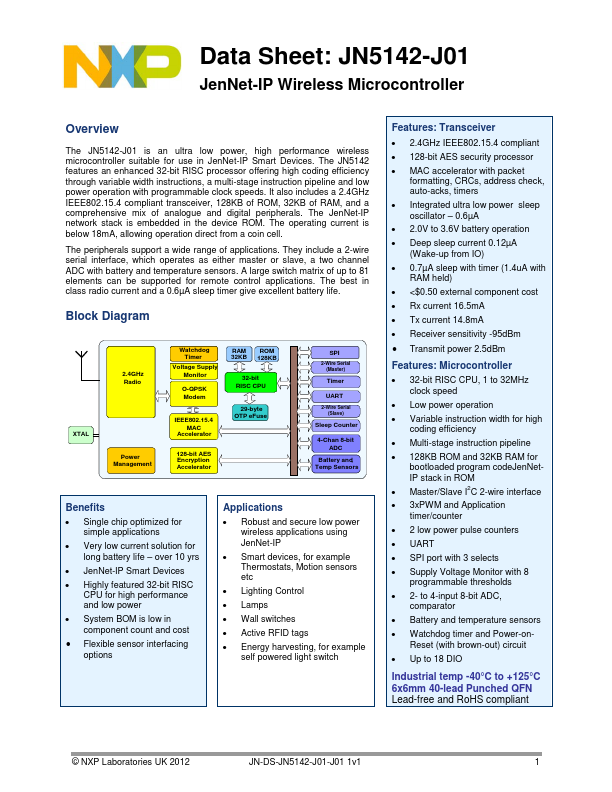

JN5142-J01 Overview

Key Features

- The JenNet-IP network stack is embedded in the device ROM

- The operating current is below 18mA, allowing operation direct from a coin cell

- The peripherals support a wide range of applications

- They include a 2-wire serial interface, which operates as either master or slave, a two channel ADC with battery and temperature sensors

- A large switch matrix of up to 81 elements can be supported for remote control applications

- The best in class radio current and a 0.6µA sleep timer give excellent battery life