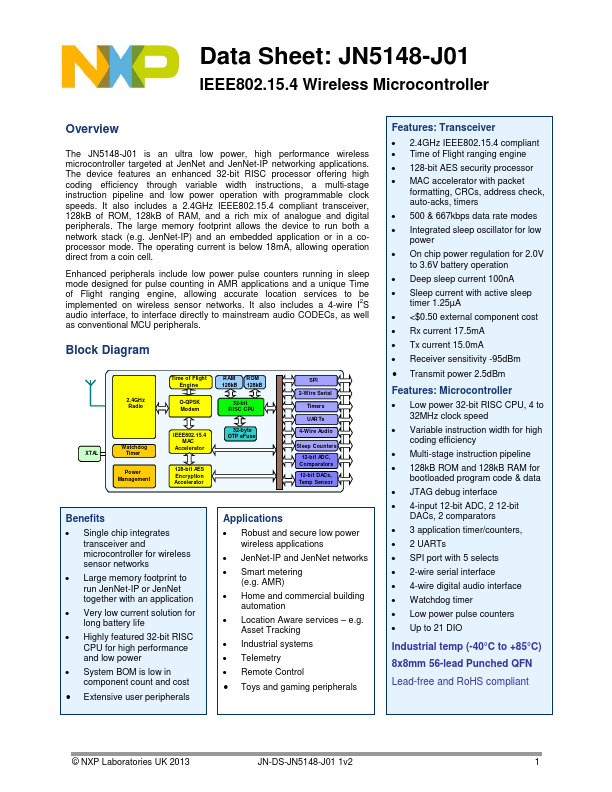

JN5148-J01 Overview

Key Features

- It also includes a 2.4GHz IEEE802.15.4 compliant transceiver, 128kB of ROM, 128kB of RAM, and a rich mix of analogue and digital peripherals

- The large memory footprint allows the device to run both a network stack (e.g

- JenNet-IP) and an embedded application or in a coprocessor mode

- The operating current is below 18mA, allowing operation direct from a coin cell

- It also includes a 4-wire I2S audio interface, to interface directly to mainstream audio CODECs, as well as conventional MCU peripherals