LPC3130

LPC3130 is (LPC3130 / LPC3131) Lowest Cost ARM9 manufactured by NXP Semiconductors.

D R A FT

D R A FT

D R A FT

R A FT

A FT

..

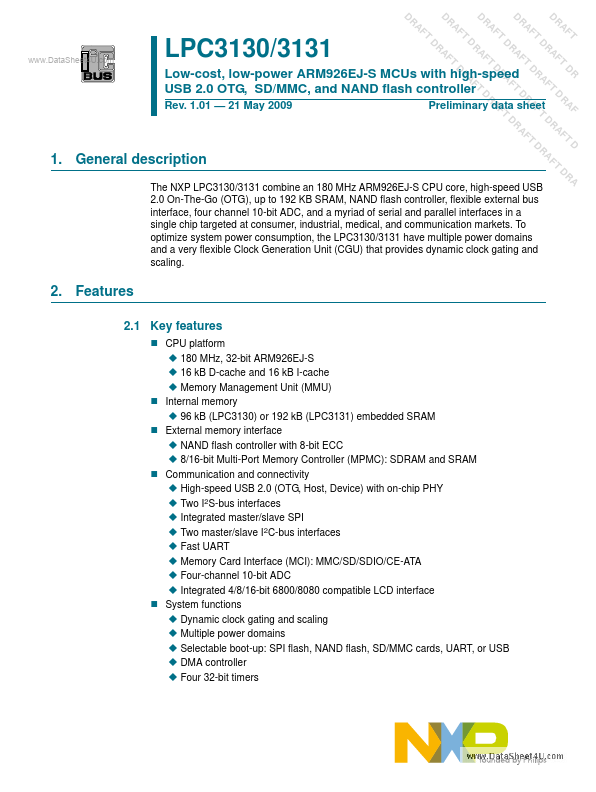

LPC3130/3131

Rev. 1.01

- 21 May 2009

Low-cost, low-power ARM926EJ-S MCUs with high-speed USB 2.0 OTG, SD/MMC, and NAND flash controller

D R R A A FT FT D R A FT D

D R A FT

D R A FT D FT D D R A R A FT

Preliminary data sheet

FT D R

R A FT D R A FT D R A F A FT D R D R

1. General description

The NXP LPC3130/3131 bine an 180 MHz ARM926EJ-S CPU core, high-speed USB 2.0 On-The-Go (OTG), up to 192 KB SRAM, NAND flash controller, flexible external bus interface, four channel 10-bit ADC, and a myriad of serial and parallel interfaces in a single chip targeted at consumer, industrial, medical, and...