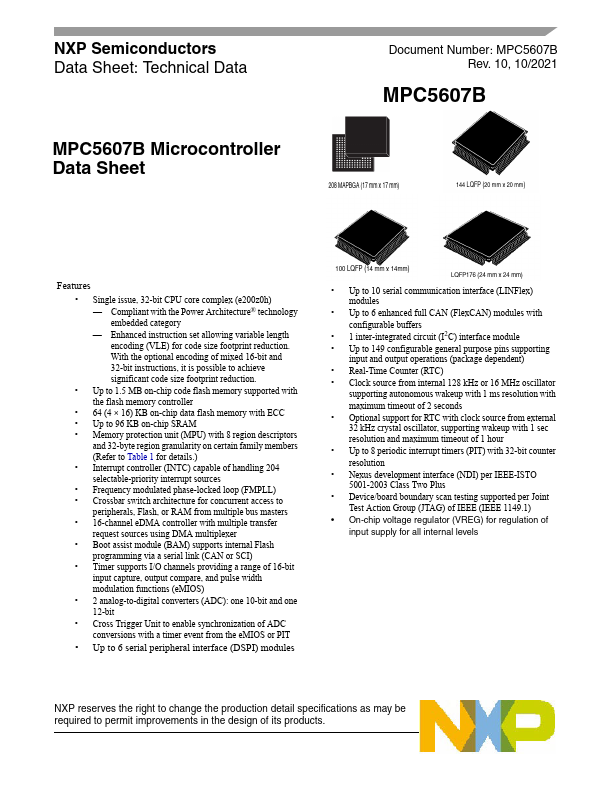

MPC5607B

Overview

- Single issue, 32-bit CPU core complex (e200z0h) - Compliant with the Power Architecture® technology embedded category - Enhanced instruction set allowing variable length encoding (VLE) for code size footprint reduction. With the optional encoding of mixed 16-bit and 32-bit instructions, it is possible to achieve significant code size footprint reduction.

- Up to 1.5 MB on-chip code flash memory supported with the flash memory controller

- 64 (4 × 16) KB on-chip data flash memory with ECC

- Up to 96 KB on-chip SRAM

- Memory protection unit (MPU) with 8 region descriptors and 32-byte region granularity on certain family members (Refer to Table 1 for details.)

- Interrupt controller (INTC) capable of handling 204 selectable-priority interrupt sources

- Frequency modulated phase-locked loop (FMPLL)

- Crossbar switch architecture for concurrent access to peripherals, Flash, or RAM from multiple bus masters

- 16-channel eDMA controller with multiple transfer request sources using DMA multiplexer

- Boot assist module (BAM) supports internal Flash programming via a serial link (CAN or SCI)