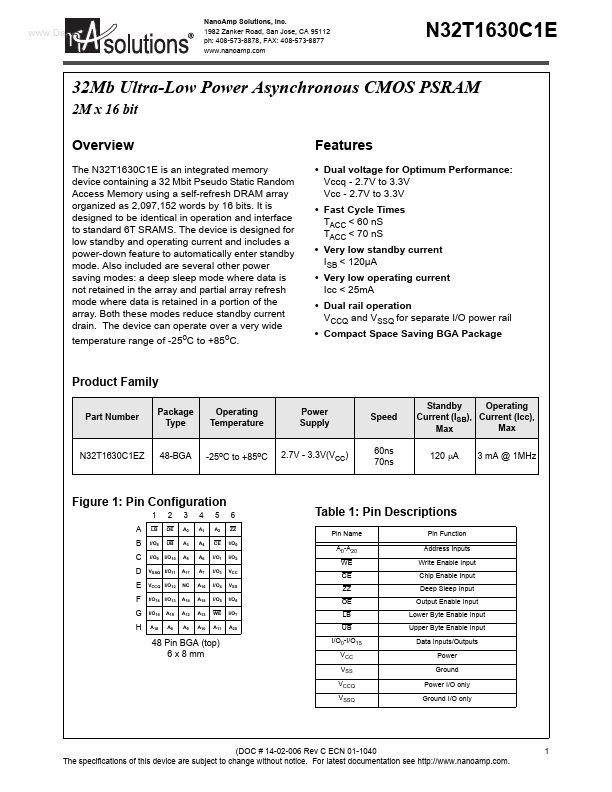

N32T1630C1E

N32T1630C1E is 32Mb Ultra-Low Power Asynchronous CMOS PSRAM manufactured by NanoAmp Solutions.

..

NanoAmp Solutions, Inc. 1982 Zanker Road, San Jose, CA 95112 ph: 408-573-8878, FAX: 408-573-8877 .nanoamp.

32Mb Ultra-Low Power Asynchronous CMOS PSRAM

2M x 16 bit Overview

The N32T1630C1E is an integrated memory device containing a 32 Mbit Pseudo Static Random Access Memory using a self-refresh DRAM array organized as 2,097,152 words by 16 bits. It is designed to be identical in operation and interface to standard 6T SRAMS. The device is designed for low standby and operating current and includes a power-down feature to automatically enter standby mode. Also included are several other power saving modes: a deep sleep mode where data is not retained...