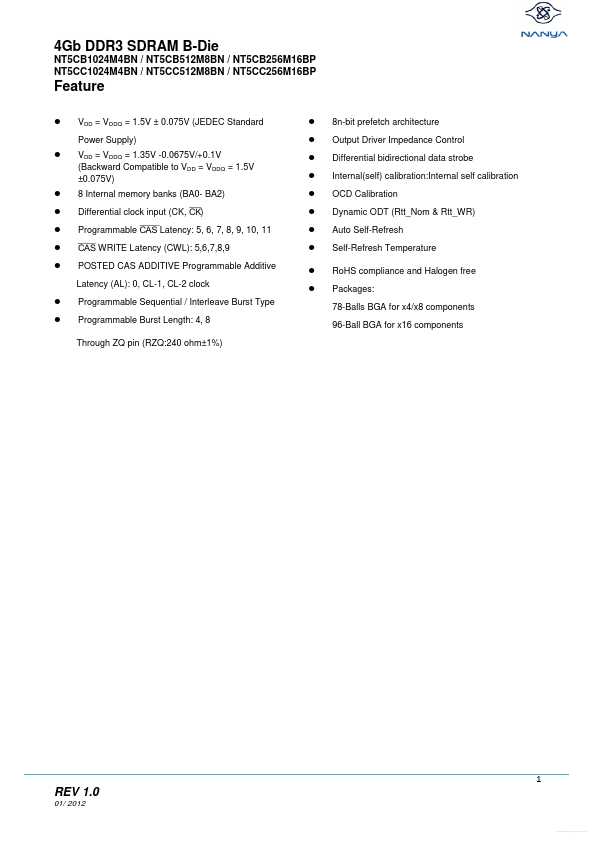

NT5CC1024M4BN Overview

Description

The 4Gb Double-Data-Rate-3 (DDR3) DRAMs is a high-speed CMOS Double Data Rate32 SDRAM containing 4,294,967,296 bits. It is internally configured as an octal-bank DRAM.

Key Features

- VDD = VDDQ = 1.5V ± 0.075V (JEDEC Standard Power Supply)

- Programmable Sequential / Interleave Burst Type Programmable Burst Length: 4, 8 Through ZQ pin (RZQ:240 ohm±1%)