NT5DS16M16ES

Overview

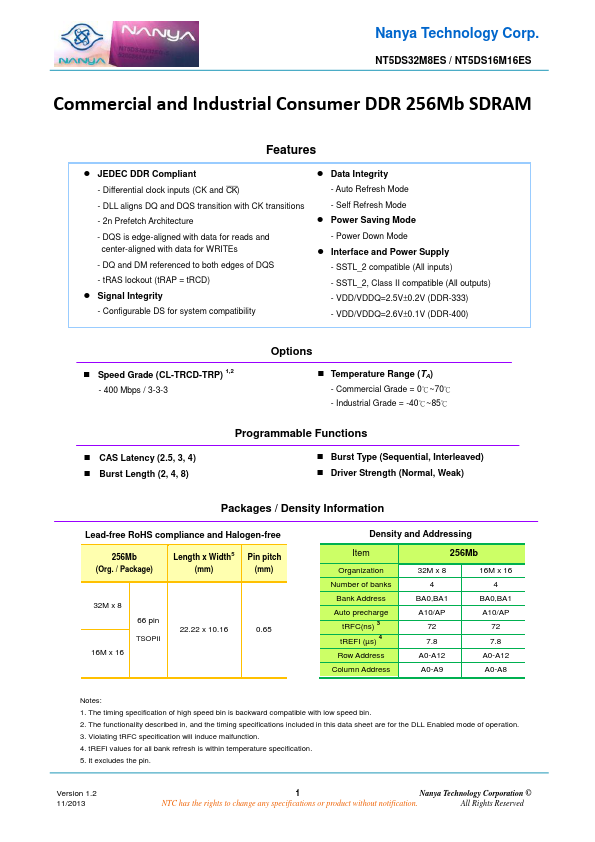

- JEDEC DDR Compliant - Differential clock inputs (CK and ) - DLL aligns DQ and DQS transition with CK transitions - 2n Prefetch Architecture - DQS is edge-aligned with data for reads and center-aligned with data for WRITEs - DQ and DM referenced to both edges of DQS - tRAS lockout (tRAP = tRCD)

- Signal Integrity - Configurable DS for system compatibility

- Data Integrity - Auto Refresh Mode - Self Refresh Mode

- Power Saving Mode - Power Down Mode

- Interface and Power Supply - SSTL_2 compatible (All inputs) - SSTL_2, Class II compatible (All outputs) - VDD/VDDQ=2.5V±0.2V (DDR-333) - VDD/VDDQ=2.6V±0.1V (DDR-400)

- Speed Grade (CL-TRCD-TRP) 1,2 - 400 Mbps / 3-3-3 Options

- Temperature Range (TA) - Commercial Grade = 0℃~70℃ - Industrial Grade = -40℃~85℃

- CAS Latency (2.5, 3, 4)

- Burst Length (2, 4, 8) Programmable Functions

- Burst Type (Sequential, Interleaved)