NT5DS16M16BG

Overview

The 256Mb DDR SDRAM is a high-speed CMOS, dynamic random-access memory containing 268,435,456 bits. It is internally configured as a quad-bank DRAM. tion may be enabled to provide a self-timed row precharge that is initiated at the end of the burst access.

- Double data rate architecture: two data transfers per clock cycle

- Bidirectional data strobe (DQS) is transmitted and received with data, to be used in capturing data at the receiver

- DQS is edge-aligned with data for reads and is centeraligned with data for writes

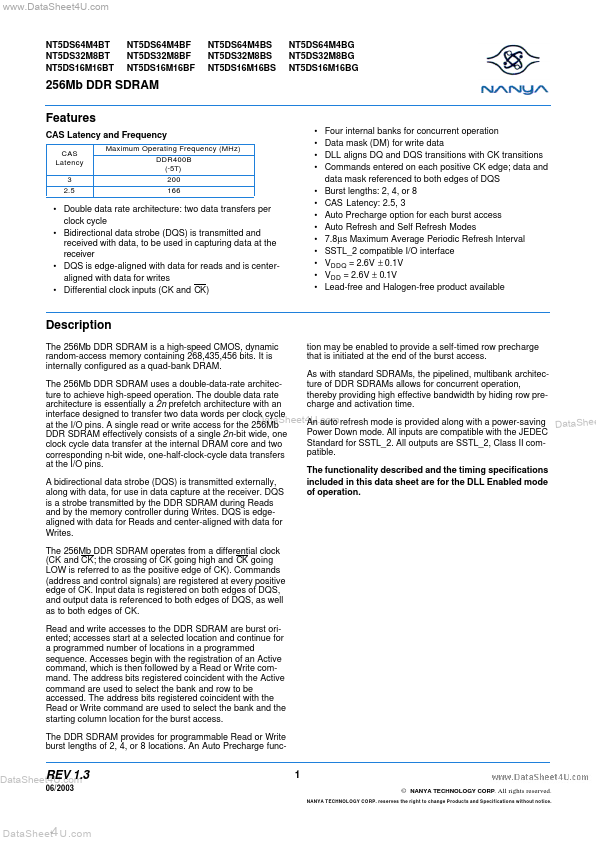

- Differential clock inputs (CK and CK) Four internal banks for concurrent operation Data mask (DM) for write data DLL aligns DQ and DQS transitions with CK transitions Commands entered on each positive CK edge; data and data mask referenced to both edges of DQS Burst lengths: 2, 4, or 8 CAS Latency: 2.5, 3 Auto Precharge option for each burst access Auto Refresh and Self Refresh Modes 7.8µs Maximum Average Periodic Refresh Interval SSTL_2 compatible I/O interface VDDQ = 2.6V ± 0.1V VDD = 2.6V ± 0.1V Lead-free and Halogen-free product available