NT5TU128M8DE-AD Overview

Description

The 1giga-bit (1Gb) Double-Data-Rate-2 (DDR2) DRAMs is a high-speed CMOS Double Data Rate 2 SDRAM containing 1,073,741,824 bits. It is internally configured as an octal-bank DRAM.

Key Features

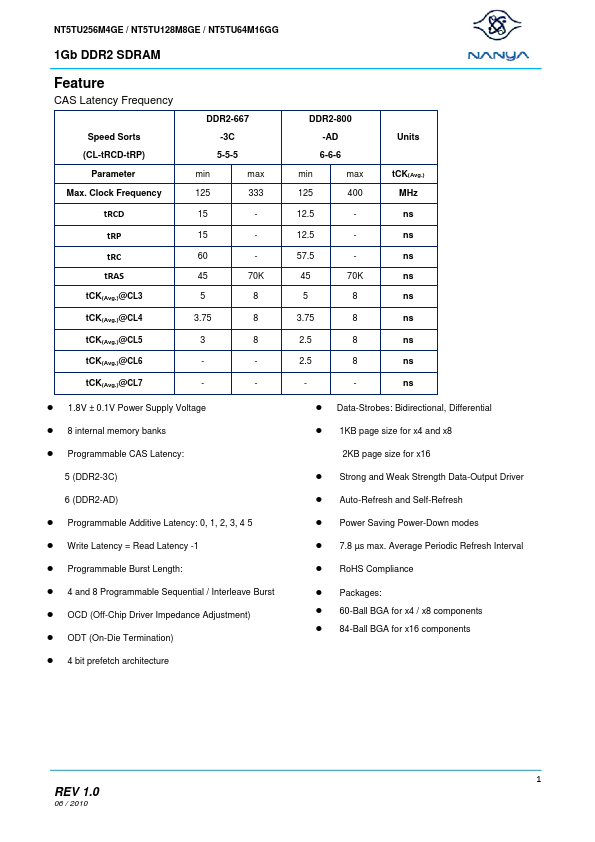

- CAS Latency Frequency DDR2-667 Speed Sorts (CL-tRCD-tRP) Parameter Max