54ACT163

54ACT163 is Synchronous Presettable Binary Counter manufactured by National Semiconductor.

- Part of the 54AC163 comparator family.

- Part of the 54AC163 comparator family.

Description

The ’AC/’ACT163 are high-speed synchronous modulo-16 binary counters. They are synchronously presettable for application in programmable dividers and have two types of Count Enable inputs plus a Terminal Count output for versatility in forming synchronous multistage counters. The ’AC/ ’ACT163 has a Synchronous Reset input that overrides counting and parallel loading and allows the outputs to be simultaneously reset on the rising edge of the clock. n n n n n n Synchronous counting and loading High-speed synchronous expansion Typical count rate of 125 MHz Outputs source/sink 24 m A ’ACT163 has TTL-patible inputs Standard Microcircuit Drawing (SMD)

- ’AC163: 5962-89582

- ’ACT163: 5962-91723

Features n ICC reduced by 50%

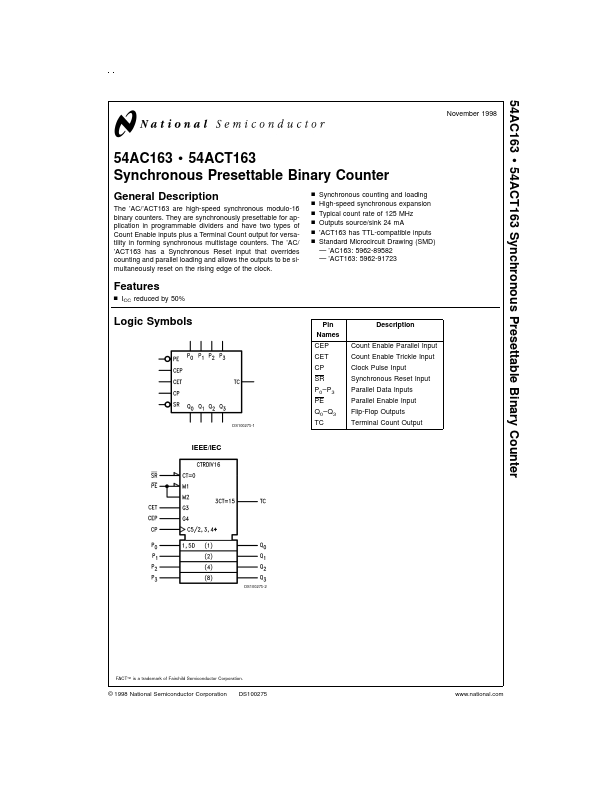

Logic Symbols

Pin Names CEP CET CP SR P0- P3 PE Q0- Q3

DS100275-1

Description

Count Enable Parallel Input Count Enable Trickle Input Clock Pulse Input Synchronous Reset Input Parallel Data Inputs Parallel Enable Input Flip-Flop Outputs Terminal Count Output

IEEE/IEC

DS100275-2

FACT™ is a trademark of Fairchild Semiconductor Corporation.

© 1998 National Semiconductor Corporation

DS100275

.national.

Connection Diagrams

Pin Assignment for DIP and Flatpak Pin Assignment for LCC

DS100275-3 DS100275-4

Functional Description

The ’AC/’ACT163 counts in modulo-16 binary sequence. From state 15 (HHHH) it increments to state 0 (LLLL). The clock inputs of all flip-flops are driven in parallel through a clock buffer. Thus all changes of the Q outputs occur as a result of, and synchronous with, the LOW-to-HIGH transition of the CP input signal. The circuits have four fundamental modes of operation, in order of precedence: synchronous reset, parallel load, count-up and hold. Four control inputs

- Synchronous Reset (SR), Parallel Enable (PE), Count Enable Parallel (CEP) and Count Enable Trickle (CET)

- determine the mode of operation, as shown in the Mode Select Table. A LOW signal on SR overrides counting and parallel loading and allows all...