Datasheet Summary

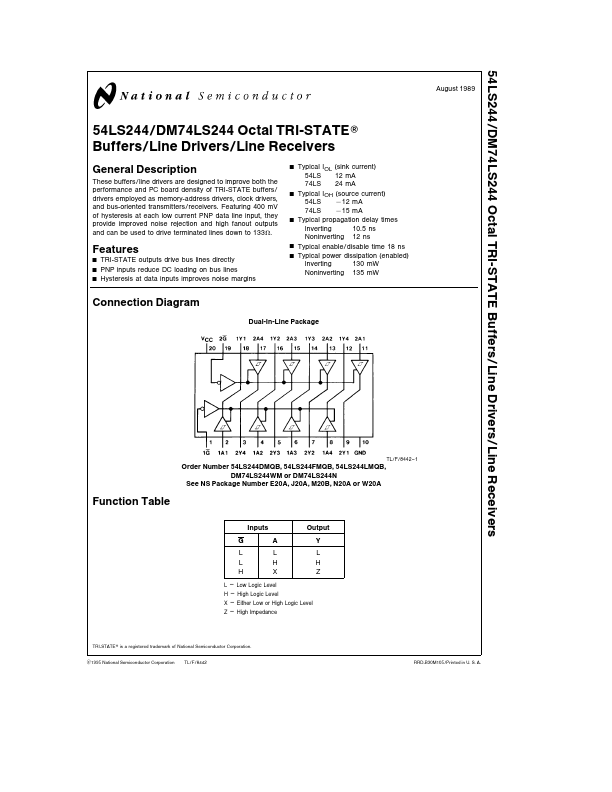

54LS244 DM74LS244 Octal TRI-STATE Buffers Line Drivers Line Receivers

August 1989

54LS244 DM74LS244 Octal TRI-STATE Buffers Line Drivers Line Receivers

General Description

These buffers line drivers are designed to improve both the performance and PC board density of TRI-STATE buffers drivers employed as memory-address drivers clock drivers and bus-oriented transmitters receivers Featuring 400 mV of hysteresis at each low current PNP data line input they provide improved noise rejection and high fanout outputs and can be used to drive terminated lines down to 133X

Features

Y TRI-STATE outputs drive bus lines directly Y PNP inputs reduce DC loading on bus lines Y Hysteresis at data...