74LVX125 Overview

Key Specifications

Package: TSSOP

Mount Type: Surface Mount

Pins: 14

Operating Voltage: 2.7 V

Description

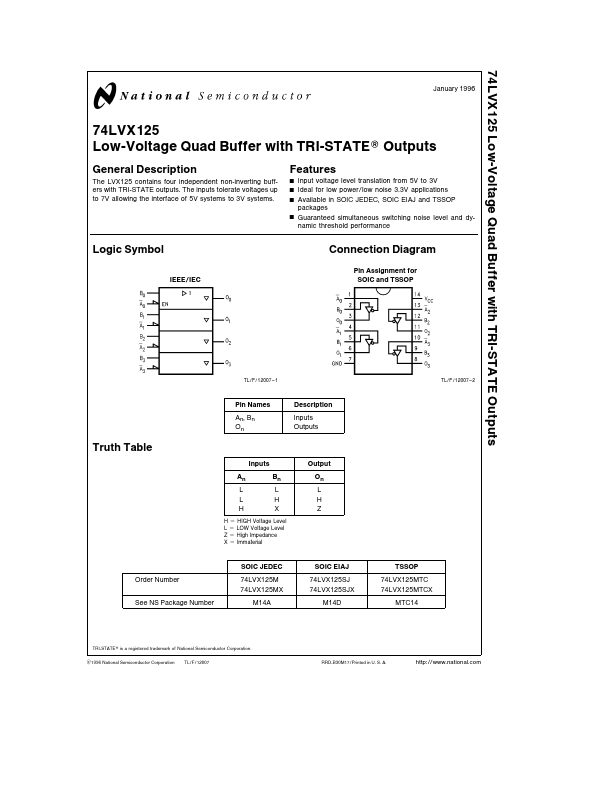

The LVX125 contains four independent non-inverting buffers with TRI-STATE outputs The inputs tolerate voltages up to 7V allowing the interface of 5V systems to 3V systems.