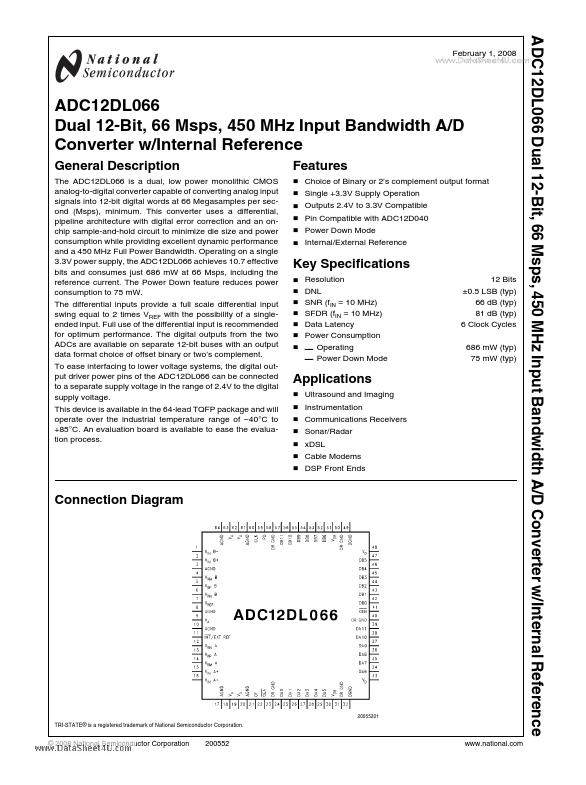

ADC12DL066 Overview

Key Specifications

Package: TQFP

Mount Type: Surface Mount

Pins: 64

Operating Voltage: 3.3 V

Description

The ADC12DL066 is a dual, low power monolithic CMOS analog-to-digital converter capable of converting analog input signals into 12-bit digital words at 66 Megasamples per second (Msps), minimum. This converter uses a differential, pipeline architecture with digital error correction and an onchip sample-and-hold circuit to minimize die size and power consumption while providing excellent dynamic performance and a 450 MHz Full Power Bandwidth.

Key Features

- Resolution DNL SNR (fIN = 10 MHz) SFDR (fIN = 10 MHz) Data Latency Po